## UNIVERSITY OF CALIFORNIA

Los Angeles

Scale-Out Packageless Processing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Saptadeep Pal

#### ABSTRACT OF THE DISSERTATION

### Scale-Out Packageless Processing

by

### Saptadeep Pal

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Los Angeles, 2021

Professor Puneet Gupta, Co-Chair

Professor Subramanian Srikantes Iyer, Co-Chair

Demand for increasing system performance is far outpacing the capability of conventional methods for performance scaling. Traditionally, performance and energy scaling has relied on transistor and silicon scaling. However, developing chips, often very large ones in the advanced technology nodes is becoming very challenging and costly. Moreover, system performance is often limited by inter-die connections. Today, dies with different functionality are packaged and integrated using PCBs. Unlike silicon features, package and PCB features have barely scaled (about 4-5x) over the past few decades. This severely limits performance and efficiency of processor systems. Moreover, next-generation of applications driven by artificial intelligence, and other data intensive applications are driving the demand for very large scale-out systems. Traditional scale-out system building and integration methodologies are failing to deliver the performance these applications demand. As a result of the above trends, future performance, power, and cost improvements cannot come from improvements in transistor technology alone. Then, how do we enable "System scaling"?

In this dissertation, first we show that packages inhibit system scaling as it reduces the potential memory bandwidth of a processor by at least one order of magnitude, allowable thermal design power (TDP) by up to 70%, and area efficiency by a factor of 5 to 18. We therefore propose *packageless processors* - processors where packages have been removed and dies directly mounted on a silicon board using a novel integration technology, Silicon Interconnection Fabric (Si-IF). We show that Si-IF-based packageless processors outperform their packaged counterparts by up to

58% (16% average), 136% (103% average), and 295% (80% average) due to increased memory bandwidth, increased allowable TDP, and reduced area respectively. We also extend the concept of packageless processing to the entire processor and memory system, where the area footprint reduction was up to 76%. To guide technology direction for dielet integration substrate technologies, we also developed a die-to-die interconnect pathfinding tool to explore the effects of physical tradeoffs such as bump pitch, wire pitch, I/O ESD capacitance etc. We show that incessant reduction of bump and wire pitch below  $10\mu m$  wouldn't be helpful for interconnect performance and we need to develop techniques and technologies to minimize reliance on large ESD structures in the chiplet I/Os as ESD capacitance starts dominating performance and energy cost of these die-to-die interconnect links. Next, we show that fine pitch chiplet integration technologies allow us to disintegrate large SoCs in to chiplets with minuscule hit in performance. This opens up the opportunity to build a chiplet eco-system, where application-optimized systems can be built by selecting a subset of chiplets from a chiplet pool. Such an eco-system however needs us to find the suitable minimal set of chiplets to build in order to target a variety of workloads efficiently. To that end, we developed the first chiplet selection framework to target a large variety of applications. We show that up to 35% improvement in EDP can be obtained from application-specific system customization and when total cost of design and manufacturing is considered, up to 72% benefit in cost is possible over SoCs.

Part 2 of the dissertation focuses on scale-out processing systems. To target scale-out systems, we propose chiplet-based waferscale processors to dramatically reduce communication overheads. The Si-IF technology can be used to build scale-out processors up to a size of an entire wafer. However, building such a large consolidated waferscale system has its own challenges. Using a waferscale GPU as a case study, we showed that while a 300 mm wafer can house about 100 GPU modules (GPMs), only a much scaled down GPU architecture with about 40 GPMs can be built when physical concerns are considered. We analyzed the design space of power-delivery network, cooling and trade-offs of yield and inter-GPM network topologies, and proposed optimized waferscale GPU architecture. We also optimized thread scheduling and data placement policies. Overall, our simulations show that an optimized waferscale architecture can provide up to 19x speedup compared to traditionally integrated systems. Then, we architected and designed a 14,336-

core shared memory waferscale system in order to understand the design challenges of waferscale processors. Several aspects of the design were built from the ground up due to the scale of the system:power delivery and on-chip regulation methods, reliable waferscale clock distribution, wafer-scale fault-tolerant network design, chiplet and waferscale system test mechanisms, and multiple physical and architectural techniques to enhance system yield. The chiplets were taped out in TSMC N40-LP process and a smaller prototype system has been functionally verified. Next, we have focused on understanding the scalability characteristics of deep learning (DL) training applications and exploring the cross-stack impact of hardware-software-technology co-design at-scale. With the aid of an optimal operation-to-device placement tool, we have proposed a framework which allows us to figure out when to use model parallelism with data parallelism instead of data parallelism alone in order to minimize end-to-end training time. Next, we developed a system-technology co-optimization tool which explores the cross-stack impact of technology scaling, model scaling and architectural innovations on end-to-end DL training time. Using this tool, we can perform rapid-yet-accurate design space exploration and find optimal architectures under given logic, memory, and inter-chip interconnect technology parameters.

Together, the techniques and methodologies developed in this dissertation lays the ground work for a revolutionary new way of thinking about system scaling. Packageless processing and scale-out waferscale architectures can indeed provide orders of magnitude improvement in performance and energy efficiency required by next-generation of applications. Moreover, the cross-stack pathfinding tools provide rapid-assessment frameworks to understand bottlenecks across different levels in the system and helps guide technology optimal decisions for processing systems.

The dissertation of Saptadeep Pal is approved.

Anthony John Nowatzki

Mani B. Srivastava

Subramanian Srikantes Iyer, Committee Co-Chair

Puneet Gupta, Committee Co-Chair

University of California, Los Angeles

2021

To my parents, brother and friends who inspire me to keep on pushing forward, and without whom none of this would have happened

## TABLE OF CONTENTS

| 1 | Intro | oductio   | n                                                                        | 1  |

|---|-------|-----------|--------------------------------------------------------------------------|----|

|   | 1.1   | A Nov     | el Heterogeneous Integration Platform for Packageless Processing         | 2  |

|   | 1.2   | Chiple    | t-based Waferscale Processing                                            | 3  |

|   | 1.3   | System    | n-Technology Co-Optimization                                             | 4  |

|   | 1.4   | Disser    | tation Outline                                                           | 5  |

| 2 | A C   | ase for l | Packageless Processors                                                   | 8  |

|   | 2.1   | Introdu   | action                                                                   | 8  |

|   | 2.2   | Packag    | ging Processors and its Limitations                                      | 10 |

|   | 2.3   | Why N     | Not Simply Remove the processor package?                                 | 14 |

|   | 2.4   | Silicon   | Interconnect Fabric: An Enabling Technology for Packageless Processing . | 16 |

|   | 2.5   | Quanti    | fying Memory Bandwidth, TDP, and Area Benefits                           | 21 |

|   |       | 2.5.1     | Baseline Processor                                                       | 21 |

|   |       | 2.5.2     | Memory Bandwidth                                                         | 21 |

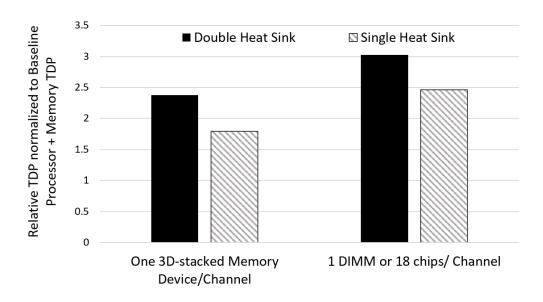

|   |       | 2.5.3     | TDP                                                                      | 23 |

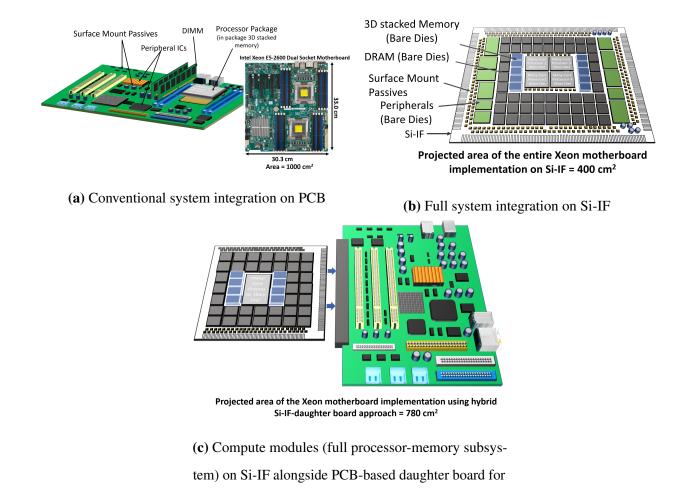

|   |       | 2.5.4     | Area                                                                     | 25 |

|   | 2.6   | Metho     | dology                                                                   | 26 |

|   | 2.7   | Results   | s                                                                        | 27 |

|   |       | 2.7.1     | Exploiting Higher Available Memory Bandwidth                             | 27 |

|   |       | 2.7.2     | Exploiting Higher Available TDP Budget                                   | 29 |

|   |       | 2.7.3     | Exploiting Higher Available Area                                         | 31 |

|   |       | 2.7.4     | Area-TDP Tradeoff                                                        | 34 |

|   | 2.8   | Discus    | sion                                                                     | 35 |

|   |      | 2.8.1 Overall System Architecture                              | 37 |

|---|------|----------------------------------------------------------------|----|

|   |      | 2.8.2 Test, Reliability, and Serviceability                    | 38 |

|   |      | 2.8.3 System Level I/O Connections and Mechanical Installation | 39 |

|   |      | 2.8.4 Manufacturing Challenges and Cost                        | 39 |

|   |      | 2.8.5 Other Architectural Implications and Use-case Scenarios  | 40 |

|   | 2.9  | Summary and Conclusions                                        | 41 |

| 3 | Path | nfinding for Chiplet Interconnect Technologies                 | 42 |

|   | 3.1  | Introduction                                                   | 42 |

|   | 3.2  | Chiplet Interconnect Pathfinding Framework                     | 45 |

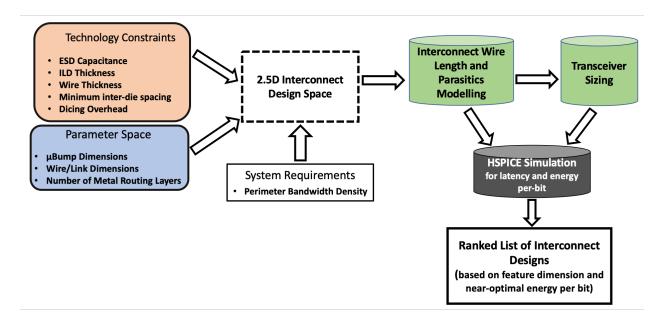

|   |      | 3.2.1 Pathfinding Flow                                         | 45 |

|   |      | 3.2.2 Interconnect Modeling                                    | 45 |

|   | 3.3  | How Should We Scale the Interconnect Substrate?                | 52 |

|   | 3.4  | Interconnects in the Chiplet Ecosystem                         | 57 |

|   | 3.5  | Discussion and Conclusions                                     | 59 |

| 4 | Desi | gn Space Exploration for Chiplet Assembly Based Processors     | 61 |

|   | 4.1  | Introduction                                                   | 61 |

|   | 4.2  | Related Work                                                   | 64 |

|   |      | 4.2.1 Processor Design Space Exploration                       | 64 |

|   |      | 4.2.2 IP-Reuse based Design                                    | 65 |

|   | 4.3  | Motivation                                                     | 65 |

|   | 4.4  | Optimal Selection of Chiplets                                  | 68 |

|   |      | 4.4.1 IntLP DSE Framework                                      | 70 |

|   |      | 4.4.2 Chiplet Assembly Cost Model                              | 73 |

|   | 4.5  | Experimental Setup                                             | 74 |

|   |      | 4.5.1     | Methodology                                            |

|---|------|-----------|--------------------------------------------------------|

|   |      | 4.5.2     | Workloads Evaluated                                    |

|   |      | 4.5.3     | Systems and Chiplets Evaluated                         |

|   |      | 4.5.4     | Cost Components and Volume                             |

|   | 4.6  | Results   | 8                                                      |

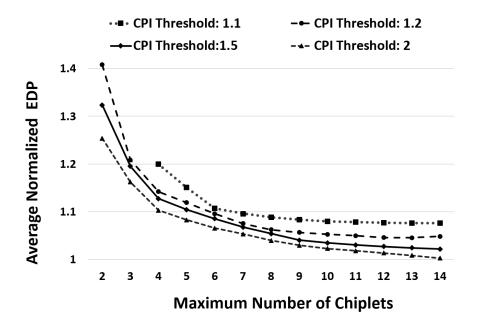

|   |      | 4.6.1     | Minimizing EDP with CPI Constraint                     |

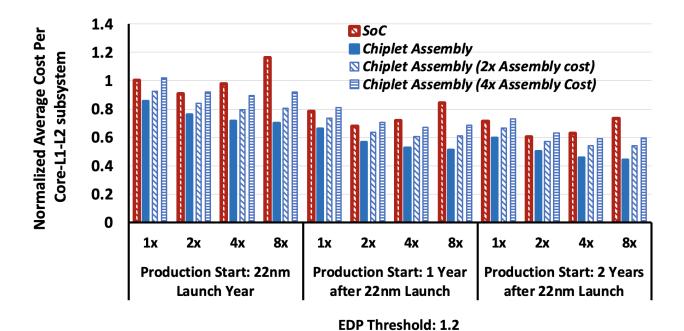

|   |      | 4.6.2     | SoC vs. Chiplet Assembly Cost Analysis                 |

|   |      | 4.6.3     | More Applications Share Chiplets than Share Systems    |

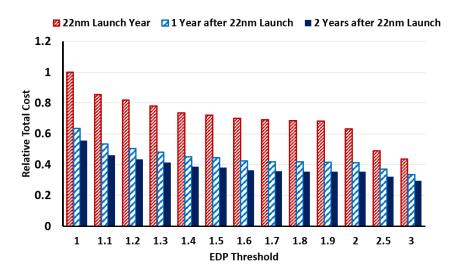

|   |      | 4.6.4     | EDP-Cost Trade-off                                     |

|   |      | 4.6.5     | Impact of Technology Maturity                          |

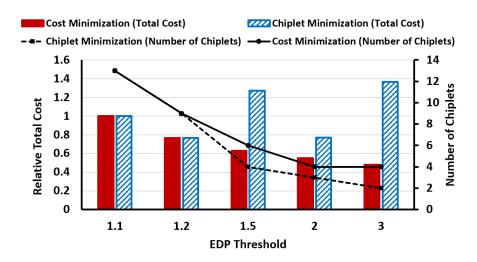

|   |      | 4.6.6     | Minimizing Number of Chiplets vs. Cost                 |

|   |      | 4.6.7     | Efficacy of Proposed Optimization Framework            |

|   |      | 4.6.8     | Optimization for Homogeneous Multi-cores               |

|   |      | 4.6.9     | Optimization of Heterogeneous CMP Systems              |

|   |      | 4.6.10    | Optimization with Heterogeneous Constraints            |

|   | 4.7  | Conclu    | sions                                                  |

| 5 | Arcl | nitecting | g Waferscale Processors - A GPU Case Study             |

|   | 5.1  | Introdu   | action                                                 |

|   | 5.2  | Backgr    | round and Technology Readiness                         |

|   | 5.3  | A Case    | e for waferscale GPU Architecture                      |

|   | 5.4  | Archite   | ecting a Waferscale GPU                                |

|   |      | 5.4.1     | Waferscale GPU Architecture under Thermal Constraints  |

|   |      | 5.4.2     | Waferscale GPU Architecture considering Power Delivery |

|   |      | 5.4.3     | Allowable Network Architectures for a Waferscale GPU   |

|   |      | 5.4.4 Overall System Architecture                     | . 113 |

|---|------|-------------------------------------------------------|-------|

|   | 5.5  | Thread Block Scheduling and Data Placement            | . 115 |

|   | 5.6  | Methodology                                           | . 119 |

|   | 5.7  | Results                                               | . 122 |

|   | 5.8  | Summary and Conclusion                                | . 127 |

| 6 | Desi | gning a 2048-Chiplet, 14336-Core Waferscale Processor | 128   |

|   | 6.1  | Introduction                                          | . 128 |

|   | 6.2  | Overview of the Waferscale Processor System           | . 130 |

|   | 6.3  | Waferscale Power Delivery and Regulation              | . 133 |

|   | 6.4  | Waferscale Clock Generation and Distribution          | . 135 |

|   | 6.5  | I/O Architecture                                      | . 139 |

|   | 6.6  | Waferscale Network Architecture and Resiliency        | . 140 |

|   | 6.7  | Testing Infrastructure                                | . 143 |

|   |      | 6.7.1 Pre-bond Testing                                | . 144 |

|   |      | 6.7.2 Post Assembly Testing                           | . 146 |

|   | 6.8  | Waferscale Substrate and its Impact on Design         | . 147 |

|   | 6.9  | Summary and Conclusion                                | . 148 |

| 7 | Opti | imizing Multi-GPU Parallelization Strategies          | 150   |

|   | 7.1  | Introduction                                          | . 150 |

|   | 7.2  | Background                                            | . 152 |

|   | 7.3  | Decomposing End-to-End Training Time                  | . 154 |

|   |      | 7.3.1 Quantifying Data Parallel Training Time         | . 155 |

|   |      | 7.3.2 Quantifying Model Parallel Training Time        | . 156 |

|   |      | 7.3.3 Hybrid Data and Model Parallel Training:        | . 157 |

|      | 7.3.4                                                  | Choosing the Best Parallelization Strategy                                                                                                                               |

|------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.4  | Metho                                                  | dology                                                                                                                                                                   |

|      | 7.4.1                                                  | System Configuration and Evaluation Points                                                                                                                               |

|      | 7.4.2                                                  | Measuring Epoch Counts to Convergence                                                                                                                                    |

|      | 7.4.3                                                  | Estimating Scaling Efficiency                                                                                                                                            |

|      | 7.4.4                                                  | Model Parallel Splitting                                                                                                                                                 |

| 7.5  | Evalua                                                 | tion                                                                                                                                                                     |

| 7.6  | Maxim                                                  | nizing MP Performance                                                                                                                                                    |

| 7.7  | Relate                                                 | d Work                                                                                                                                                                   |

|      | 7.7.1                                                  | Hybrid Parallelization                                                                                                                                                   |

|      | 7.7.2                                                  | Orthogonal Parallelization Strategies                                                                                                                                    |

|      | 7.7.3                                                  | Alternate Techniques to Improve DP Scaling                                                                                                                               |

|      | 7.7.4                                                  | Reinforcement Learning-based Device Placement                                                                                                                            |

|      | 7.7.5                                                  | Framework Support                                                                                                                                                        |

| 7.8  | Conclu                                                 | asion                                                                                                                                                                    |

| Deei | oFlow:                                                 | A Cross-Stack Pathfinding Framework for Distributed AI Systems 177                                                                                                       |

| 8.1  | •                                                      | uction                                                                                                                                                                   |

| 8.2  |                                                        | ntion                                                                                                                                                                    |

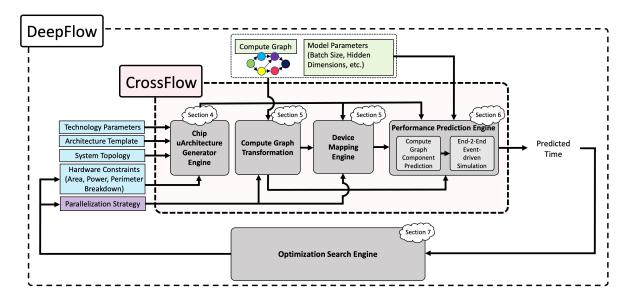

| 8.3  |                                                        | low Overview                                                                                                                                                             |

|      | 8.3.1                                                  | CrossFlow Building Blocks                                                                                                                                                |

|      | 8.3.2                                                  | Search and Optimization Engine (SOE)                                                                                                                                     |

|      |                                                        | Parallelism Strategy Space                                                                                                                                               |

| 8.4  |                                                        | itecture Generator Engine                                                                                                                                                |

|      |                                                        | Technology Components Library                                                                                                                                            |

|      | 7.5<br>7.6<br>7.7<br>7.8<br><b>Dee</b> j<br>8.1<br>8.2 | 7.4 Metho 7.4.1 7.4.2 7.4.3 7.4.4 7.5 Evalua 7.6 Maxim 7.7 Relate 7.7.1 7.7.2 7.7.3 7.7.4 7.7.5 7.8 Conclu  DeepFlow: 8.1 Introdu 8.2 Motiva 8.3 DeepF 8.3.1 8.3.2 8.3.3 |

| 1.3    | Hardware Resource Allocation                                                                                     |

|--------|------------------------------------------------------------------------------------------------------------------|

| 1.4    | Micro-architectural Parameter Generation                                                                         |

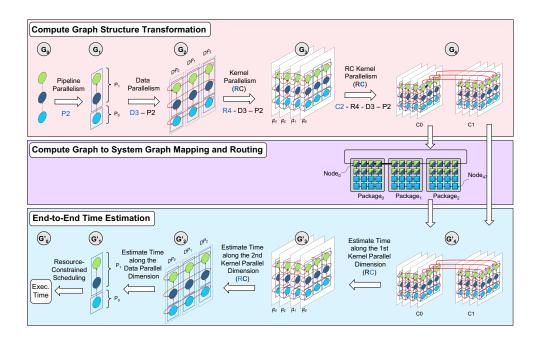

| mpu    | te Graph Transformation and Device Mapping Engine                                                                |

| 5.1    | Compute Graph Structure Transformation                                                                           |

| 5.2    | Device Mapping and Routing Engine                                                                                |

| rforn  | nance Prediction Engine                                                                                          |

| 5.1    | Hierarchical Roofline                                                                                            |

| 5.2    | Memory Hierarchy Modeling                                                                                        |

| 5.3    | DataFlow Model                                                                                                   |

| 5.4    | Inter/Intra-Package Communication Modeling                                                                       |

| 5.5    | End-to-End Time Estimation                                                                                       |

| esign  | Space Exploration Engine                                                                                         |

| lidati | on                                                                                                               |

| se St  | udies                                                                                                            |

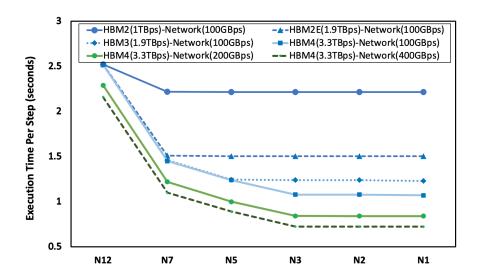

| 9.1    | Impact of Technology Scaling                                                                                     |

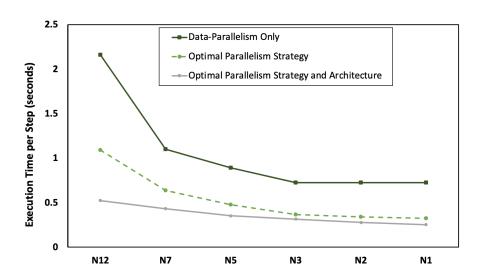

| 9.2    | Co-optimizing Technology, Parallelism Strategy and Hardware Architecture                                         |

|        | Design                                                                                                           |

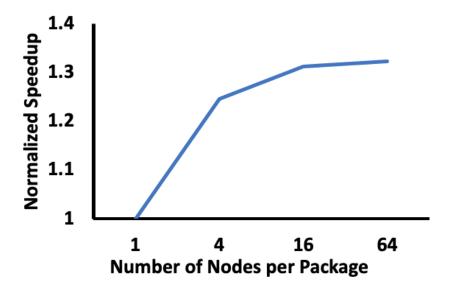

| 9.3    | Effect of Multi-Node Package                                                                                     |

| nclus  | sion                                                                                                             |

| sion   |                                                                                                                  |

| ervie  | ew of Contributions                                                                                              |

| 1.1    | Packageless Processors                                                                                           |

| 1.2    | Pathfinding for Chiplet Integration Technologies                                                                 |

|        | i.4<br>ompui<br>5.1<br>5.2<br>rform<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>esign<br>lidati<br>se St<br>0.1<br>0.2 |

|         | 9.1.3  | Chiplet Selection for Application-specific System                       |

|---------|--------|-------------------------------------------------------------------------|

|         | 9.1.4  | Waferscale GPU Architecture                                             |

|         | 9.1.5  | Design Methodologies for Chiplet-based Waferscale Systems 207           |

|         | 9.1.6  | Multi-GPU Deep Learning Parallelization Strategies                      |

|         | 9.1.7  | DeepFlow                                                                |

| 9.2     | Direct | ions for Future Work                                                    |

|         | 9.2.1  | Waferscale Memory and Networking Systems                                |

|         | 9.2.2  | Fault Modelling, Design-for-Test and Physical Design Infrastructure for |

|         |        | Chiplet Assemblies                                                      |

| Referen | ices   |                                                                         |

## LIST OF FIGURES

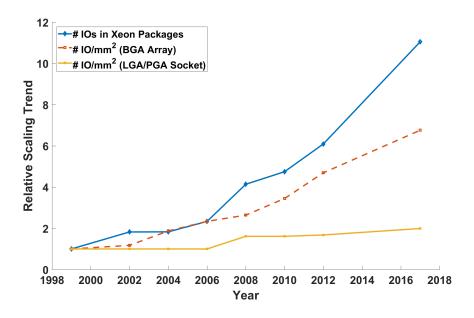

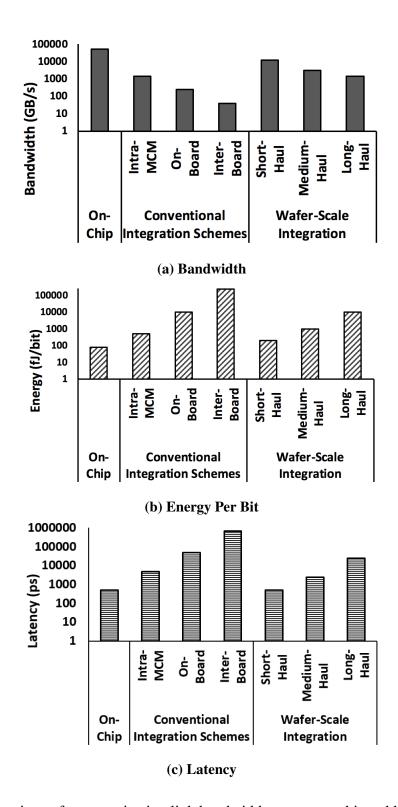

| 2.1  | I/O demand is growing faster than the I/O pin density scaling                                                        | 12 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

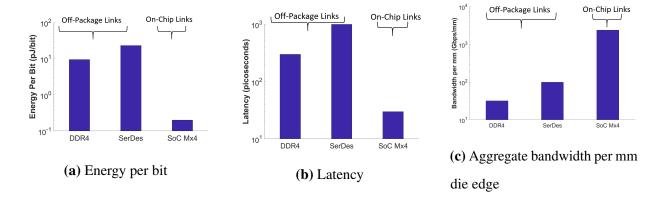

| 2.2  | Comparison of communication link energy, latency and bandwidth for on-chip versus                                    |    |

|      | off-package links                                                                                                    | 13 |

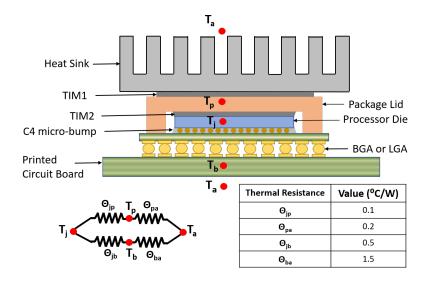

| 2.3  | Cross-section of a packaged die with heat sink placed on a PCB is shown, alongside the                               |    |

|      | thermal resistance model. $T_a$ , $T_p$ , $T_j$ , $T_b$ denotes the ambient, package lid, chip-junction,             |    |

|      | PCB temperature respectively. The thermal resistance values for a typical processor                                  |    |

|      | package is shown alongside. [1,2]                                                                                    | 15 |

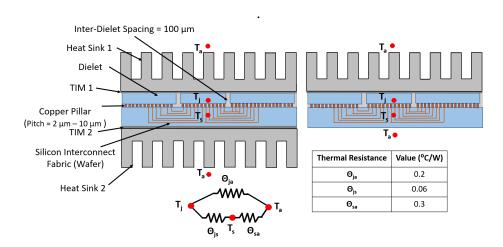

| 2.4  | Cross-section of an Si-IF system, alongside the thermal resistance model. $T_a$ , $T_j$ , $T_s$                      |    |

|      | denote the ambient, chip-junction and silicon substrate temperatures respectively. Heat                              |    |

|      | sink can be directly attached to the top of the dielets or both at the top and bottom of the                         |    |

|      | Si-IF.The thermal resistance values for a typical system on Si-IF is shown alongside [1–3]                           | 15 |

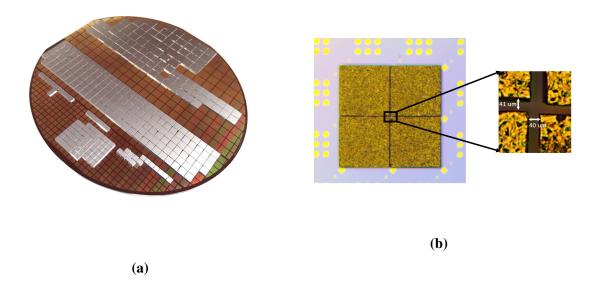

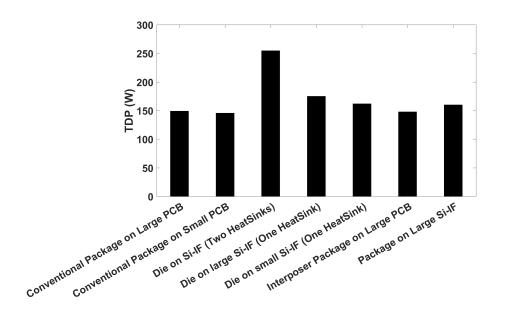

| 2.5  | (a) Wafer scale interconnect fabric partially populated with eighty 4 mm <sup>2</sup> , one hundred                  |    |

|      | and seventy one 9 mm <sup>2</sup> , fifty eight 16 mm <sup>2</sup> and forty one 25 mm <sup>2</sup> dies bonded on a |    |

|      | 4-inch silicon wafer. Copper pillar pitch of 10 $\mu$ m is used. (b) Micrograph showing                              |    |

|      | four dies bonded on to an Si-IF with ${\sim}40~\mu m$ inter-die spacing. (c) Serpentine test                         |    |

|      | structure with copper pillars on the Si-IF and landing bond pad on the bare dies [4]                                 | 19 |

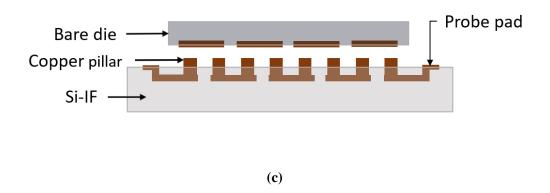

| 2.6  | Base Processor Architecture Overview                                                                                 | 23 |

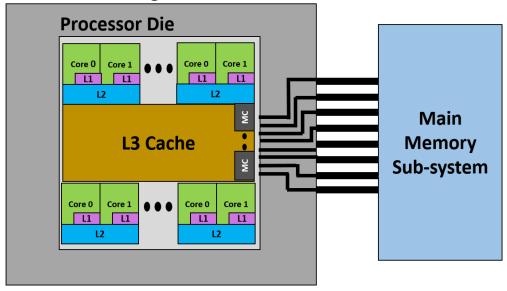

| 2.7  | Maximum achievable TDP of the baseline processor system in various integration                                       |    |

|      | schemes                                                                                                              | 25 |

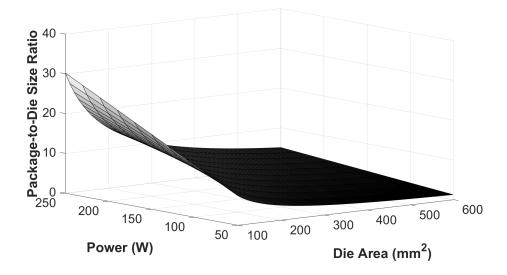

| 2.8  | Sensitivity analysis of area benefit from removing the package                                                       | 26 |

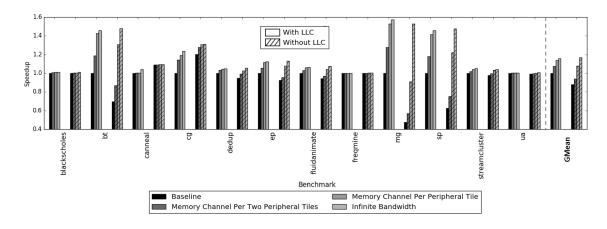

| 2.9  | Performance benefit from increased number of memory channels with and without L3.                                    | 28 |

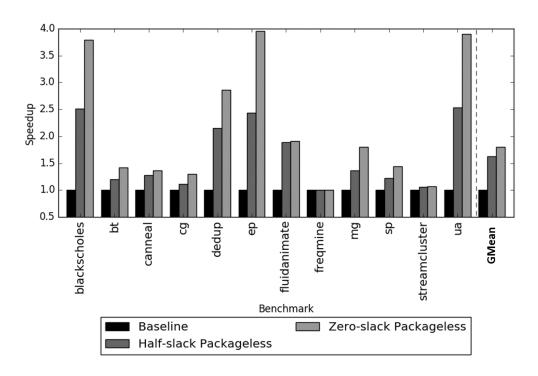

| 2.10 | Performance benefits of utilizing TDP slack                                                                          | 31 |

| 2.11 | Performance increase by exploiting area slack                                                                        | 32 |

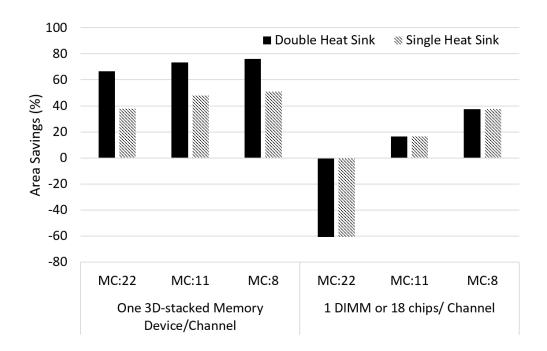

| 2.12 | Area savings when implementing processor-memory subsystem on Si-IF. 22, 11 and                                                    |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|      | 8 memory controller configuration on Si-IF are compared against baseline packaged                                                 |    |

|      | configuration with 8 channels of off-package DRAM                                                                                 | 33 |

| 2.13 | TDP of implementing the baseline processor-memory subsystem on Si-IF of size of                                                   |    |

|      | total processor and memory package area normalized to baseline processor system TDP.                                              | 33 |

| 2.14 | Illustration of a conventional PCB based system and different integration schemes using                                           |    |

|      | Si-IF                                                                                                                             | 36 |

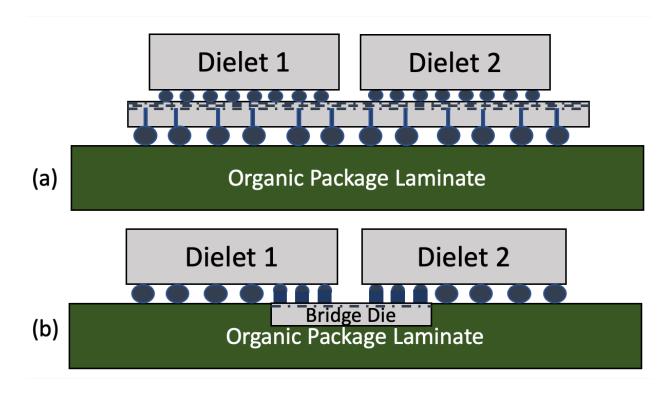

| 3.1  | Cross-section view of two 2.5D substrates: (a) Silicon Interposer [5,6], (b) EMIB [7] 4                                           | 14 |

| 3.2  | Chiplet interconnect pathfinding framework                                                                                        | 46 |

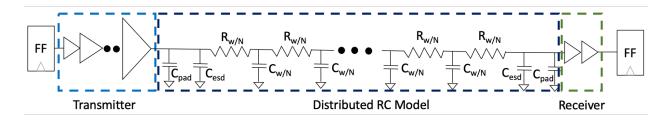

| 3.3  | Distributed wire model for interconnect link. $C_{pad}$ is the pad/ $\mu$ bump capacitance, $C_{esd}$                             |    |

|      | is the capacitance introduced by the ESD protection circuitry, $R_{w/N}$ and $C_{w/N}$ are the                                    |    |

|      | wire segment resistance and capacitance respectively                                                                              | 46 |

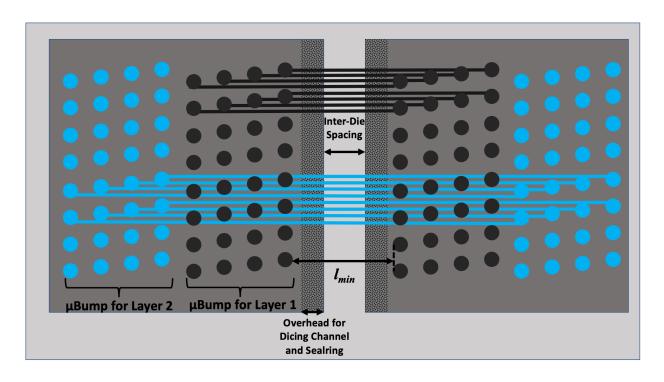

| 3.4  | Top-down view of two dies on a 2.5D substrate with $\mu$ bumps and interconnect wiring                                            |    |

|      | on multiple layers                                                                                                                | 48 |

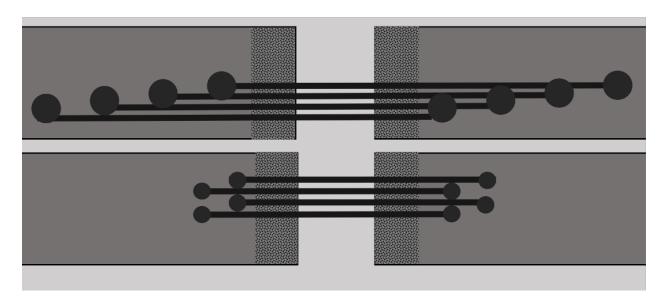

| 3.5  | Smaller $\mu$ bumps help reduce the interconnect length                                                                           | 48 |

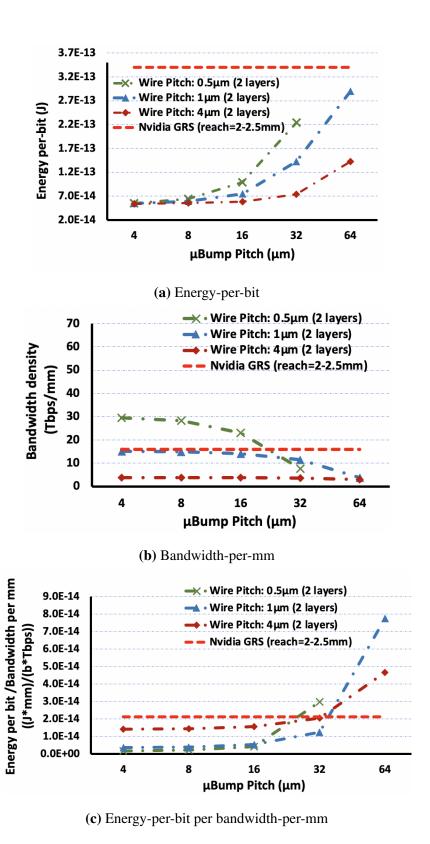

| 3.6  | Scaling of energy-per-bit, bandwidth-per-mm and their ratio with $\mu$ bump pitch and                                             |    |

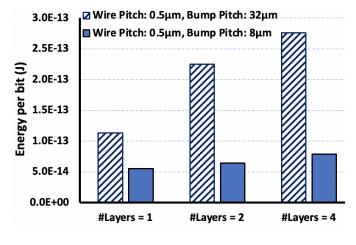

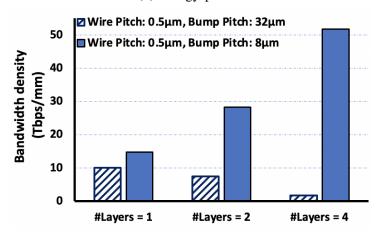

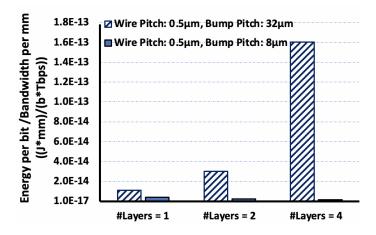

|      | wire pitch for two metal routing layers ( $C_{esd}$ =50fF, $l_{min}$ =150 $\mu m$ )                                               | 19 |

| 3.7  | Scaling of energy-per-bit, bandwidth-per-mm and their ratio with metal routing layers                                             |    |

|      | for fixed wire pitch and two different $\mu$ bump pitch values ( $C_{esd}$ =50fF, $l_{min}$ =150 $\mu$ m) 5                       | 50 |

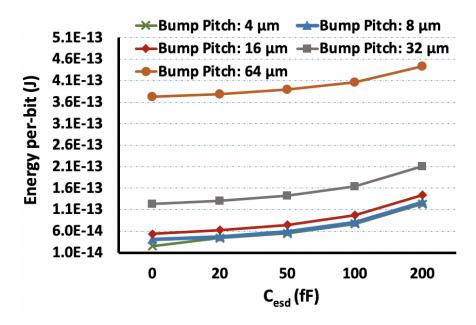

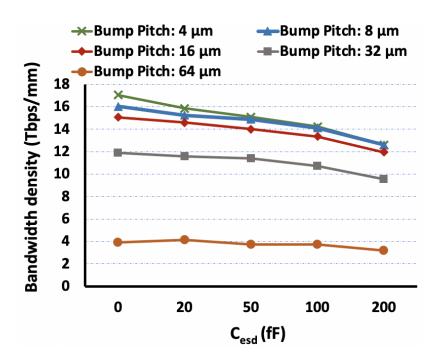

| 3.8  | Energy-per-bit scaling with $C_{esd}$ and $\mu$ bump pitch ( $l_{min}$ =150 $\mu$ m, $wire_{pitch}$ =1 $\mu$ m, $N_{layers}$ =2). | 55 |

| 3.9  | Bandwidth density scaling with $C_{esd}$ and $\mu$ bump pitch ( $l_{min}=150\mu m$ , $wire_{pitch}=1\mu m$ ,                      |    |

|      | $N_{layers}$ =2)                                                                                                                  | 56 |

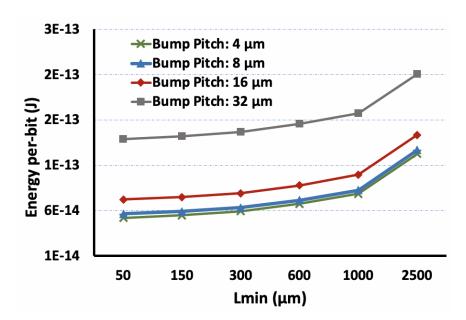

| 3.10 | Energy-per-bit scaling with $l_{min}$ and $\mu$ bump pitch ( $C_{esd}$ =50fF, $wire_{pitch}$ =1 $\mu$ m, $N_{layers}$ =           |    |

|      | 2)                                                                                                                                | 57 |

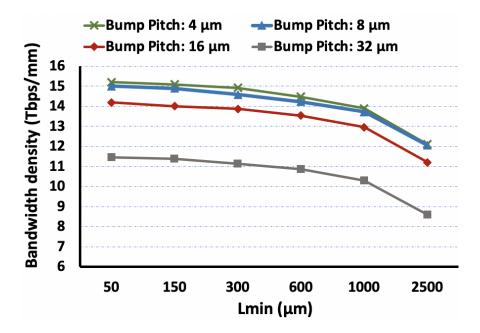

| 3.11 | Bandwidth density scaling with $l_{min}$ and $\mu$ bump pitch ( $C_{esd}$ =50fF, $wire_{pitch}$ =1 $\mu m$ ,                      |    |

|      | $N_{lovers}$ =2)                                                                                                                  | 58 |

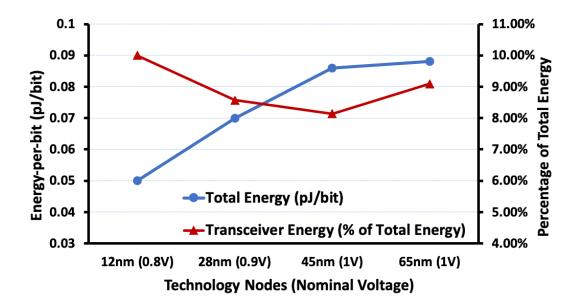

| 3.12 | Total link energy and transceiver energy as % of total energy for for dielets (transceiver |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | circuitry) from four different technology nodes. Link length: 1.5mm, W/S: $0.5\mu m$ ,     |    |

|      | $C_{esd}$ :50fF                                                                            | 59 |

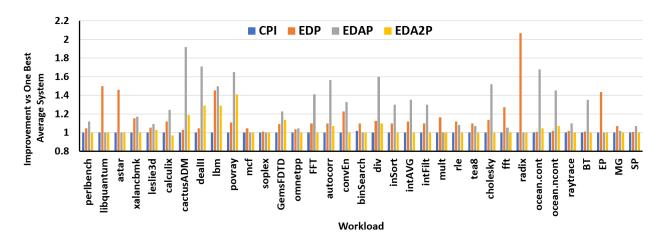

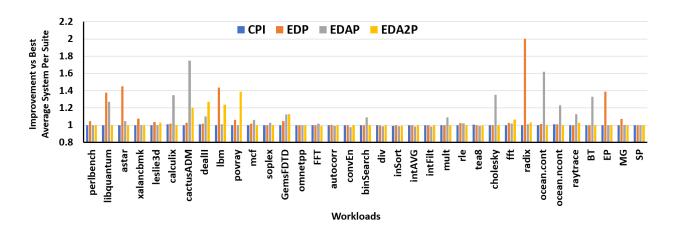

| 4.1  | Benefit of assigning each workload its best processor vs a processor optimized across      |    |

|      | all workloads                                                                              | 66 |

| 4.2  | Benefit of assigning four processors optimized across all workloads vs four processors     |    |

|      | each optimized for one of the four benchmark suites                                        | 66 |

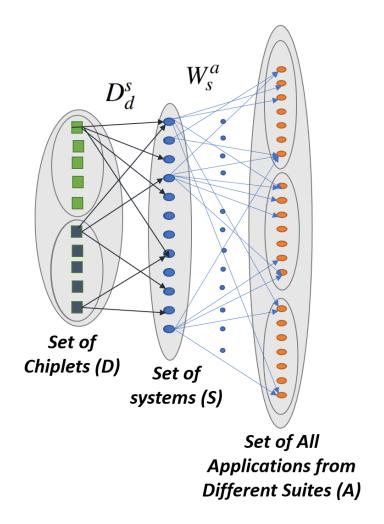

| 4.3  | Illustration of the multi-chiplet selection problem                                        | 68 |

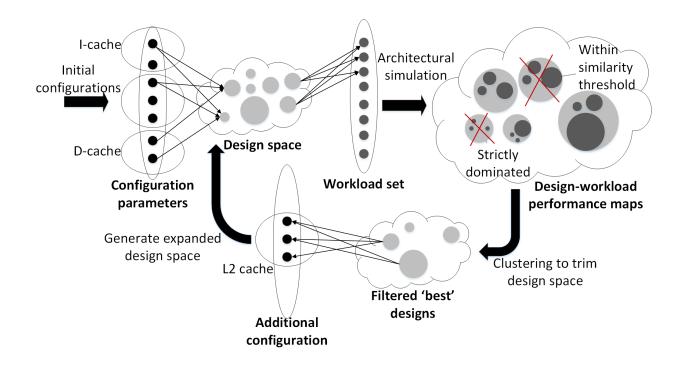

| 4.4  | Experimental methodology for design space generation                                       | 69 |

| 4.5  | Pareto curve showing average normalized EDP vs maximum number of chiplets allowed          |    |

|      | in the optimization. We show the pareto curves for different CPI thresholds                | 81 |

| 4.6  | Curve showing cost benefits of chiplet based assembly over SoC for different sizes of      |    |

|      | the system and technology maturity level                                                   | 83 |

| 4.7  | Curve showing trade-off for EDP and total cost at different technology maturity level      | 84 |

| 4.8  | Curve showing the difference between minimizing the number of chiplets versus total        |    |

|      | cost. The experiments were done for system size of 1x and production during 22nm           |    |

|      | launch year                                                                                | 86 |

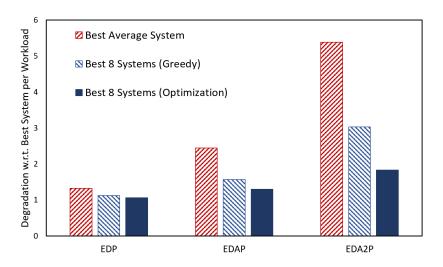

| 4.9  | Comparison between different system selection approaches for each metric when              |    |

|      | compared to the baseline case of best custom system per workload                           | 87 |

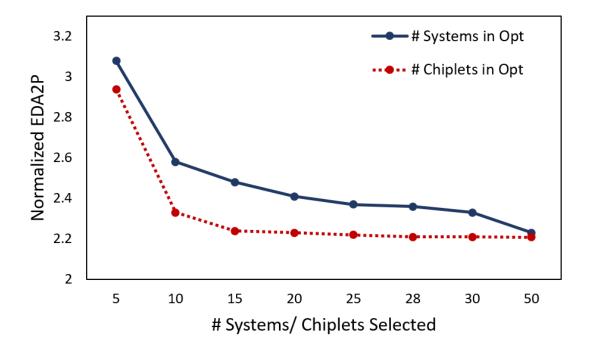

| 4.10 | Benefit in EDA $^2$ P (normalized CPI threshold = 1.2) for Heterogeneous CMP is shown      |    |

|      | for the cases where number of systems (SoCs) is taken into consideration versus when       |    |

|      | number of chiplets is considered in the optimization                                       | 88 |

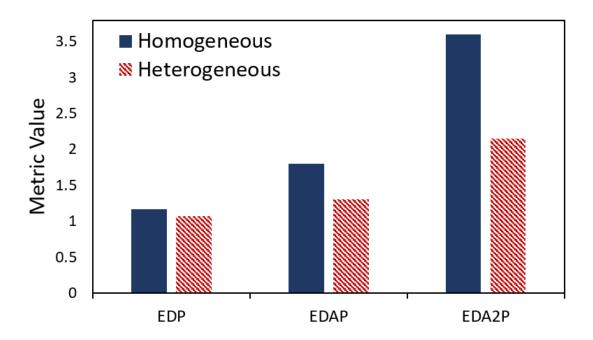

| 4.11 | Average normalized metric values are snown for nomogeneous and neterogeneous                         |

|------|------------------------------------------------------------------------------------------------------|

|      | constraints in area and CPI for different metrics for 5 systems. For heterogeneous                   |

|      | constraints, normalized CPI thresholds are 1.2 for SPLASH-2 and NPB, 1.6 for SPEC                    |

|      | and 2.4 for EEMBC. Area thresholds are 15 mm <sup>2</sup> for EEMBC, 25 mm <sup>2</sup> for SPEC and |

|      | no area constraint for SPLASH and NPB. Homogeneous constraints impose no area                        |

|      | threshold and normalized CPI threshold 1.2 for all suites                                            |

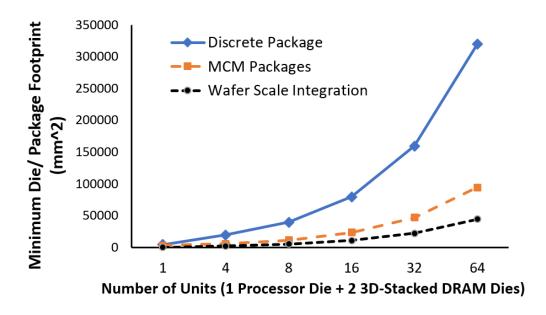

| 5.1  | Minimum die/package footprint for different integration schemes are shown for increas-               |

|      | ing number of processor dies per system                                                              |

| 5.2  | Comparison of communication link bandwidth, energy per bit and latency for on-chip                   |

|      | links and different types of links in conventional integration schemes and waferscale                |

|      | integration scheme                                                                                   |

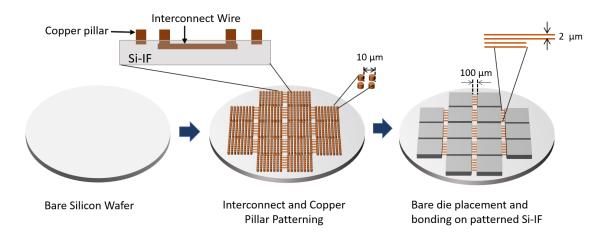

| 5.3  | The system assembly process flow is shown. Interconnect layers and copper pillars                    |

|      | are made by processing the bare silicon wafer. Bare dies are then bonded on the wafer                |

|      | using TCB                                                                                            |

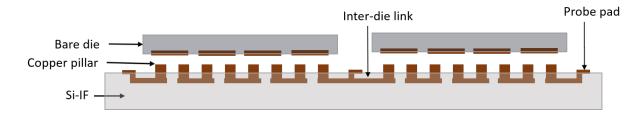

| 5.4  | Schematic of the prototype with interconnection between the serpentine structure of                  |

|      | two different dies is shown                                                                          |

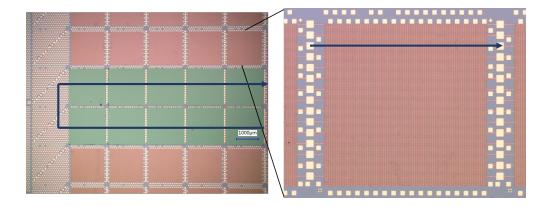

| 5.5  | Micrograph of the prototype with inter-die connectivity is shown. Ten 4 mm <sup>2</sup> dies         |

|      | are bonded and tested for continuity of a signal across the dies. Each die has rows of               |

|      | serpentine structure as shown in the schematic. A zoomed-in picture of the Si-IF is also             |

|      | shown with 40,000 copper pillars                                                                     |

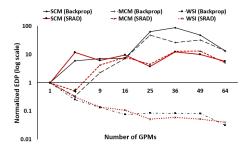

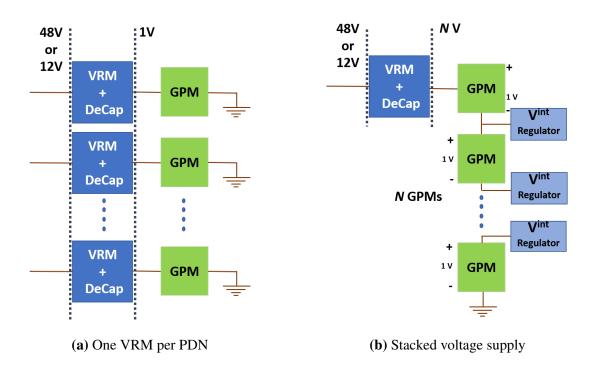

| 5.6  | Normalized EDP for Backprop and SRAD                                                                 |

| 5.7  | Normalized Execution Time for Backprop and SRAD                                                      |

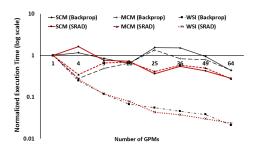

| 5.8  | Schematic cross-section of a waferscale system on Si-IF, alongside the thermal re-                   |

|      | sistance model. Ta, Tj, Ts denote the ambient, chip-junction and silicon substrate                   |

|      | temperatures respectively. Two heat sinks one directly attached to the dies and another              |

|      | backside heatsink covering the Si-IF substrate is shown. The thermal resistance values               |

|      | for a 300 mm <sup>2</sup> waferscale system with heatsinks are also shown [8] 106                    |

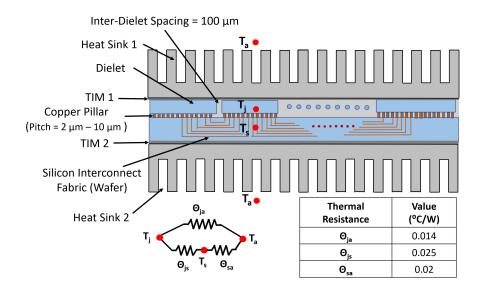

| 5.9  | PDN schemes                                                                            |

|------|----------------------------------------------------------------------------------------|

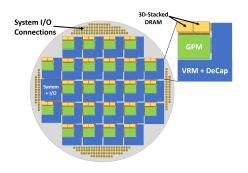

| 5.10 | Waferscale GPU with 25 GPM units (1 redundant unit) comprising of two 3D-stacked       |

|      | DRAM per unit, VRM unit and decoupling capacitors                                      |

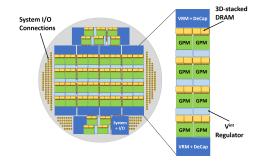

| 5.11 | Waferscale GPU with 42 GPM units (2 redundant units) comprising of two 3D-stacked      |

|      | DRAM per unit, VRM unit and decoupling capacitors                                      |

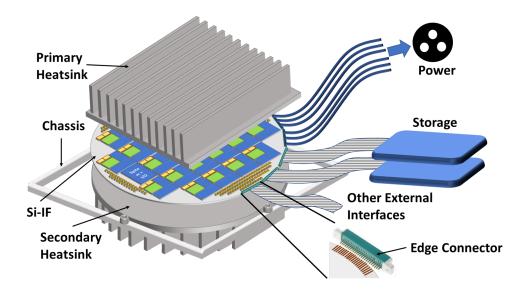

| 5.12 | An Si-IF system assembly is shown with the primary and backside secondary heat         |

|      | sinks. The whole system is bolted to a chassis. The host CPU could either be connected |

|      | externally or reside on the wafer itself                                               |

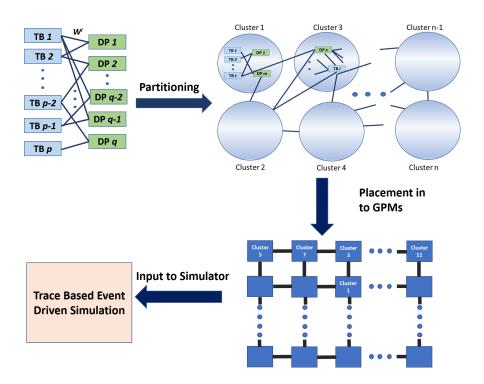

| 5.13 | TB and DRAM page partitioning and physical GPM mapping flow                            |

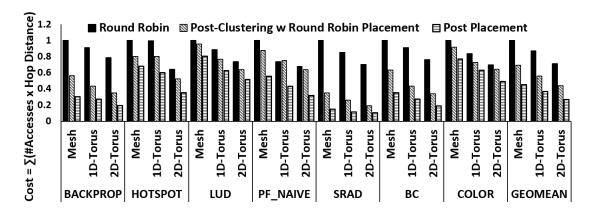

| 5.14 | Improvement in the access cost metric from offline partitioning and GPM placement      |

|      | is shown. Baseline is data locality aware distributed scheduling and first touch data  |

|      | placement                                                                              |

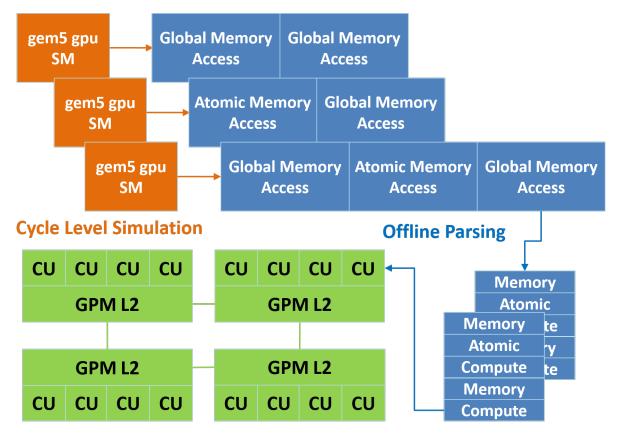

| 5.15 | Simulator Workflow                                                                     |

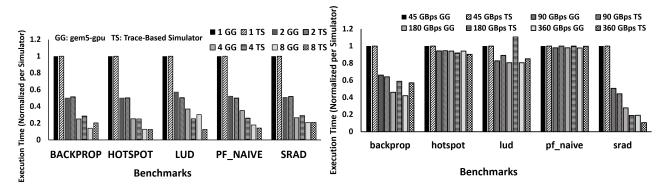

| 5.16 | CU Scaling for Gem5-GPU and Trace-based Simulator                                      |

| 5.17 | DRAM Bandwidth Scaling for Gem5-GPU and Trace-based Simulator for 8 CUs 120            |

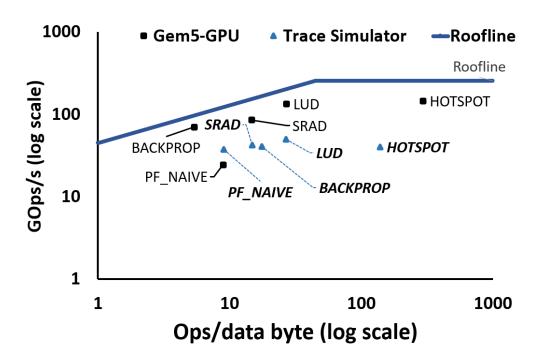

| 5.18 | Roofline Plot Comparison between Gem5-GPU and our Trace Simulator                      |

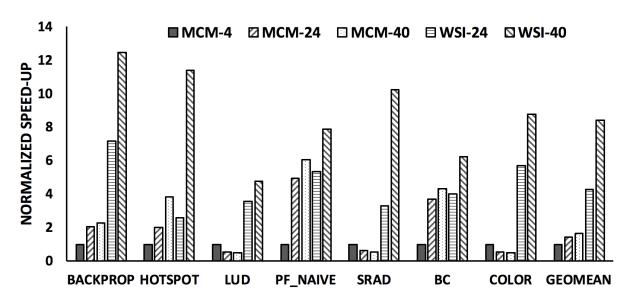

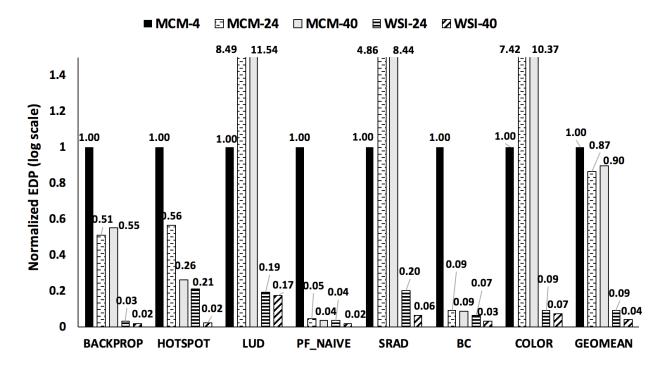

| 5.19 | Performance improvement for Waferscale GPUs vs MCM package based conventional          |

|      | systems                                                                                |

| 5.20 | EDPs for waferscale GPUs vs MCM package based conventional systems                     |

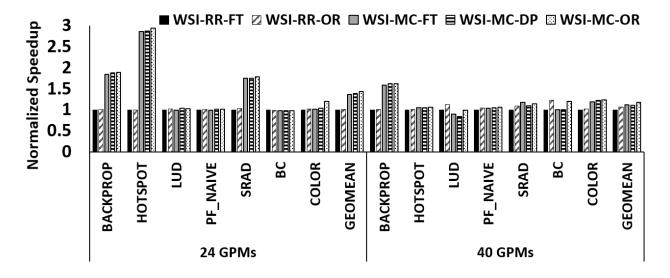

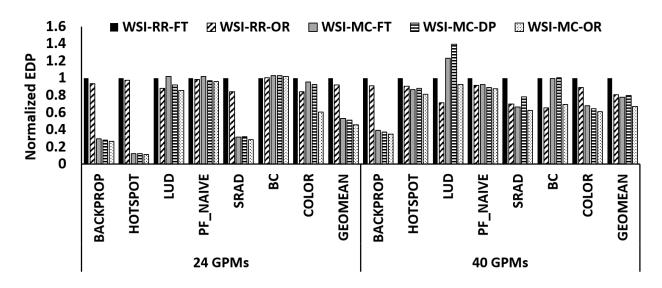

| 5.21 | Performance of different scheduling and data placement policies                        |

| 5.22 | EDP of different scheduling and data placement policies                                |

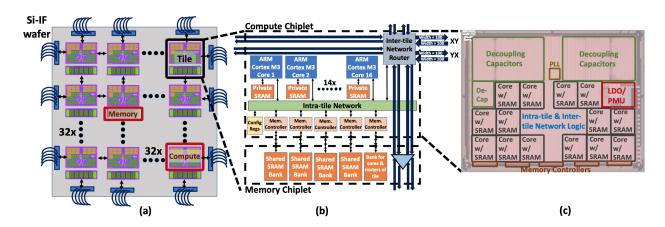

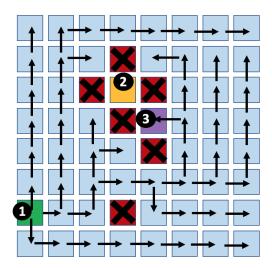

| 6.1  | (a) Waferscale Processor System Overview showing 32x32 tile array where each tile      |

|      | comprises of a compute chiplet and a memory chiplet. (b) Detailed overview of the      |

|      | compute and memory chiplets. (c) Micrograph of the compute chiplet                     |

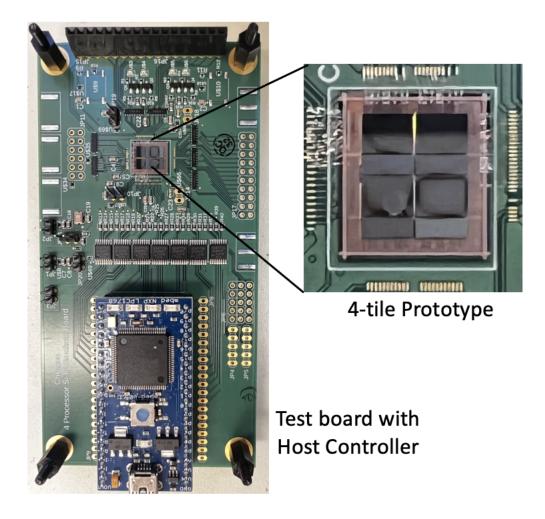

| 6.2  | A 4-tile prototype system is shown                                                     |

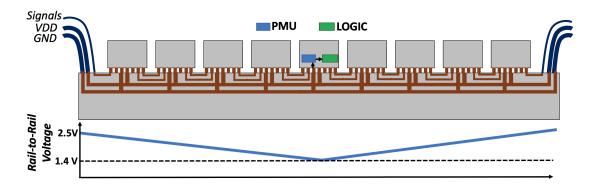

| 6.3  | Power is delivered from the edge. The chiplets at the edge of the wafer receive power    |

|------|------------------------------------------------------------------------------------------|

|      | at 2.5V. There is voltage droop as we move towards the center of the wafer and the       |

|      | chiplets at the center receive power at 1.4V                                             |

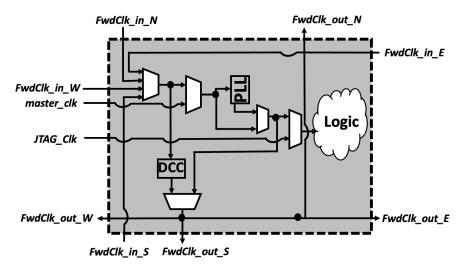

| 6.4  | Schematic of clock selection and forwarding circuitry                                    |

| 6.5  | A clock forwarding configuration is shown for a system with faulty tiles. All tiles      |

|      | except the yellow one can receive the forwarded clock                                    |

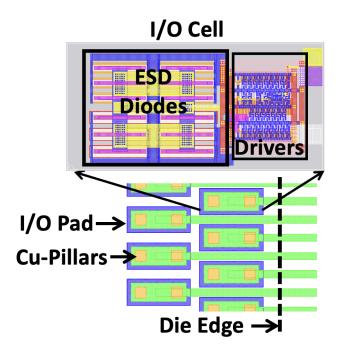

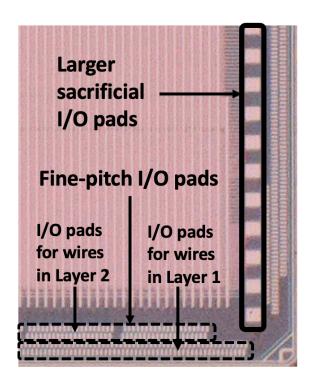

| 6.6  | Fine-pitch I/O layout with ESD protection circuitry and two Cu-pillars per I/O pad 137   |

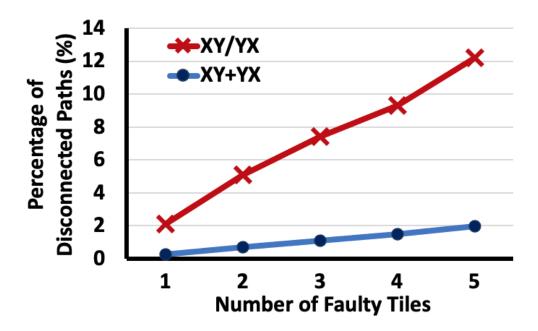

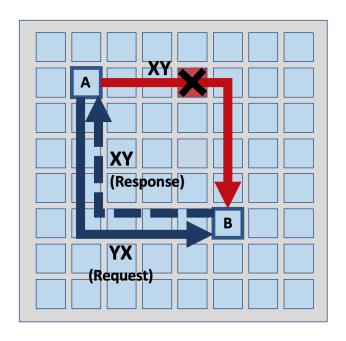

| 6.7  | Average percentage of disconnected source-destination pairs for the conventional         |

|      | scheme with one DoR network versus when two networks are used. This result is            |

|      | obtained using a set of randomly generated fault maps                                    |

| 6.8  | Fault-tolerant waferscale mesh network architecture                                      |

| 6.9  | Larger pads are for probing and fine-pitch pads are for inter-chiplet communication 142  |

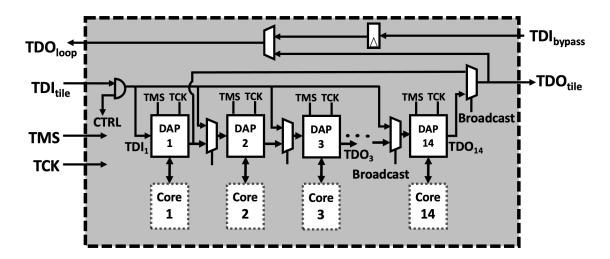

| 6.10 | Schematic of the test circuitry inside a tile                                            |

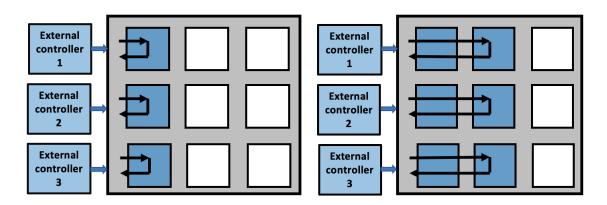

| 6.11 | Progressive unrolling scheme is shown. The JTAG chain is unrolled progressively to       |

|      | identify the faulty chiplet in the chain                                                 |

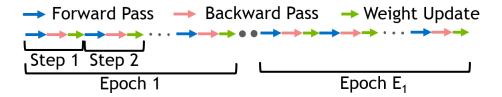

| 7.1  | Deep learning training flow                                                              |

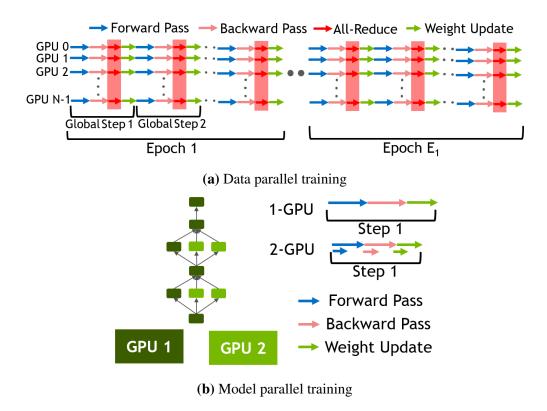

| 7.2  | Different Training Parallelization Strategies                                            |

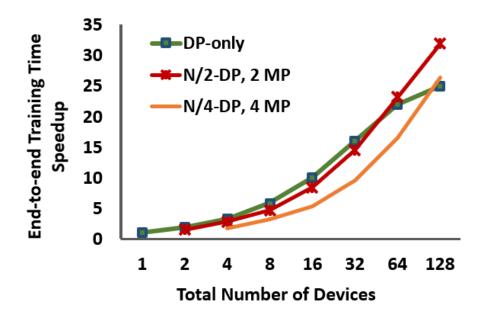

| 7.3  | An example plot showing the speedup obtained from DP alone, and the hybrid strategy.     |

|      | <i>N</i> refers to the total number of devices used for training                         |

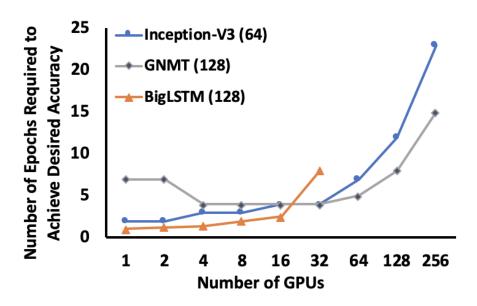

| 7.4  | Number of epochs required for the networks to converge versus increasing global batch    |

|      | size with increase in the number of GPUs. We emulated larger global batch sizes          |

|      | corresponding to large number of GPUs using the technique described in Section 7.4.2 162 |

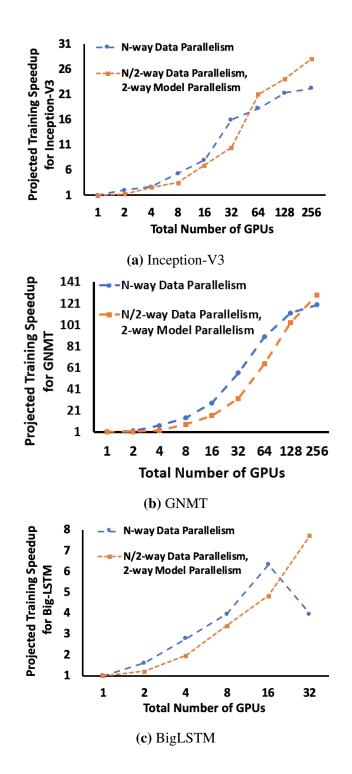

| 7.5  | Projected speedup of hybrid MP-DP parallelization vs DP-only parallelization 163         |

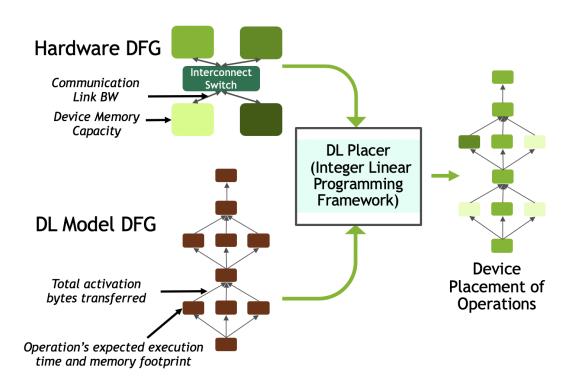

| 7.6  | DLPLacer Flow Diagram                                                                    |

| 7.7  | DLPlacer's placement solution for Inception-V3. Different colors denote different        |

|      | devices                                                                                  |

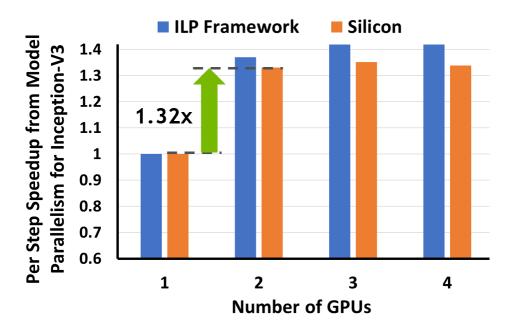

| 7.8  | Normalized per-step speedup from model parallelism as estimated by DLPiacer and                       |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | obtained from silicon experiments for the Inception-V3 network                                        | 172 |

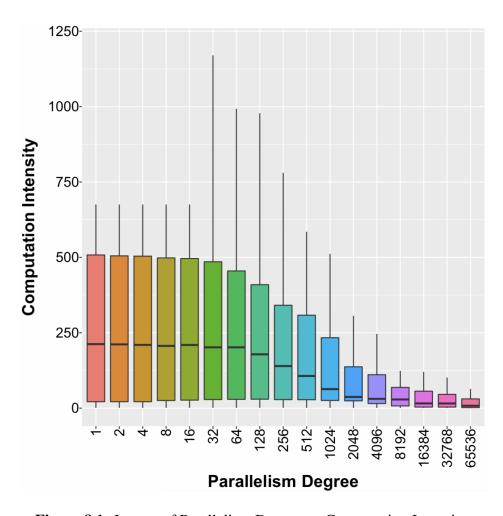

| 8.1  | Impact of Parallelism Degree on Computation Intensity                                                 | 180 |

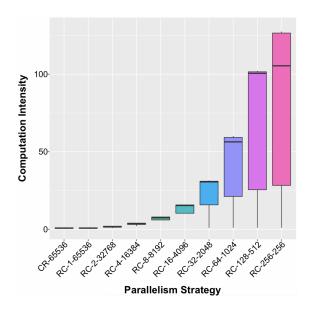

| 8.2  | Impact of Parallelism Strategy on Computation Intensity                                               | 180 |

| 8.3  | DeepFlow Overview.                                                                                    | 181 |

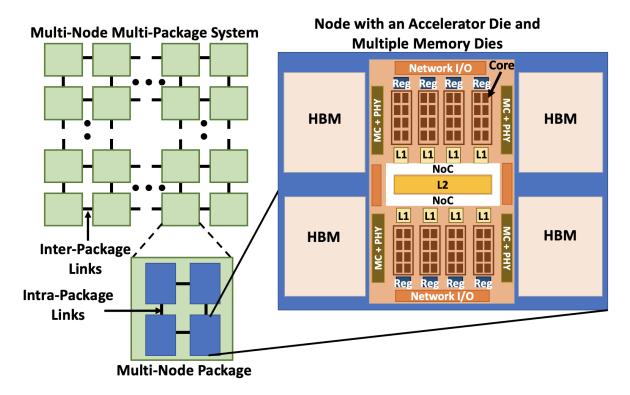

| 8.4  | Architecture Template: Overview of a hardware system whose characteristics can be                     |     |

|      | configured in DeepFlow.                                                                               | 187 |

| 8.5  | An Example of a Compute Graph Transformation, Device Mapping and Routing, and End-to-                 |     |

|      | End Time Estimation: (top) Cross-edges are shown in red. We only show a subset of cross-edges         |     |

|      | for kernel parallelism. Blue solid borderlines indicates separate hardware nodes. At every            |     |

|      | parallelization stage, black hashed lines show graph replication along that dimension. A replica      |     |

|      | is a graph with a similar structure, however, the kernel size and/or data size could be different for |     |

|      | each replica. The original graph is a simple 3-layer feed-forward neural network that is divided      |     |

|      | into two sub-graphs (P2). Then for each pipeline stage, batch size is distributed across three        |     |

|      | workers (D3). Then for each data shard of each pipeline stage, the kernels are distributed in a       |     |

|      | row-column fashion across a 4×2 torus (RC-K4-K2). (middle) Mapping a 4-D hyper-cube into              |     |

|      | a 2-D mesh: a greedy layout mapped in the following order: kernel(R), kernel(C), pipeline and         |     |

|      | data. The bolded black edge in G4 is mapped onto a 4-hop path in the system graph. (bottom)           |     |

|      | backward pass time estimation                                                                         | 193 |

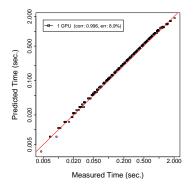

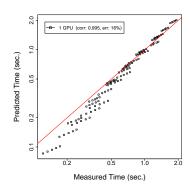

| 8.6  | GEMM Validation on P4                                                                                 | 197 |

| 8.7  | GEMM Validation on DGX                                                                                | 197 |

| 8.8  | LM Validation on V100.                                                                                | 197 |

| 8.9  | Technology Scaling: Effect of scaling different logic, memory and network technologies                |     |

|      | is shown.                                                                                             | 200 |

| 8.10 | Co-optimizing parallelism strategy and hardware architecture design                                   | 201 |

| 8.11 | Performance improvement from multi-node package                                                       | 201 |

## LIST OF TABLES

| 2.1 | Package-to-Die Size ratio                                                          |

|-----|------------------------------------------------------------------------------------|

| 2.2 | Analysis of board level I/O availability                                           |

| 2.3 | Configuration of the many-core baseline processor                                  |

| 2.4 | Comparison of Si-IF vs other 2.5D technologies                                     |

| 2.5 | Increasing Frequency or Number of Tiles to Exploit Available TDP Slack 30          |

| 2.6 | Area Slack Exploitation Parameters                                                 |

| 3.1 | Parameter values used in our analysis                                              |

| 4.1 | Notations                                                                          |

| 4.2 | Workloads Evaluated                                                                |

| 4.3 | System parameters and their values                                                 |

| 4.4 | Normalized Cost components at different Technology Nodes                           |

| 5.1 | Yield of Si-IF for different number of metal layers                                |

| 5.2 | GPU Topologies                                                                     |

| 5.3 | No of supportable GPMs for different junction temperatures                         |

| 5.4 | Number of Layers Required vs Supply Voltage to the Wafer. $10\mu m$ thick metal is |

|     | available in most technologies which support RF                                    |

| 5.5 | VRM & Decap Overhead Per GPM                                                       |

| 5.6 | Proposed PDN solutions                                                             |

| 5.7 | Operating Voltage and Frequency for the 41 GPMs with 12 V supply and 4-GPMs per    |

|     | stack                                                                              |

| 5.8 | Inter-GPM Network Topologies                                                       |

| 5.9 | Benchmarks                                                                         |

| 6.1 | Salient Features of the Waferscale Processor System                         |

|-----|-----------------------------------------------------------------------------|

| 7.1 | MP splitting strategy and the speedup obtained when split across 2 GPUs 166 |

| 7.2 | Summary of notations used in the ILP                                        |

| 8.1 | Different technology components                                             |

#### **ACKNOWLEDGMENTS**

This dissertation is the culmination of many years of hard work, the support and guidance of my advisors and the doctoral committee, and the love and encouragement of my family and friends. This journey has been a roller-coaster ride, from being a fresh undergraduate student to finishing my masters and subsequently the doctoral program. Tough times lead to sleepless nights, but the results of the continued perseverance at solving problems and coming up with new solutions has been nothing less than mind-boggling. Now, standing at the end of the tunnel, I can definitely say that the last six years of investment has been worth the returns. Overall, this experience has been extremely fulfilling and I owe gratitude to a number of people without whom my doctoral studies would not have been possible.

I would first like to thank my doctoral committee: Profs. Puneet Gupta (chair and advisor), Subramanian S. Iyer (co-chair and co-advisor), Mani Srivastava, and Tony Nowatzki for their outstanding teaching and research guidance. Prof. Gupta has been a great advisor, mentor and a sounding board. I am grateful to him for the constant support, patience, guidance and providing me with all the resources. This dissertation would not have been possible without his excellent help and foresight. He helped me in becoming a successful researcher. I would like to thank Prof. Subramanian (Subu) S. Iyer for being an instrumental co-advisor who introduced me to the world of electronics packaging. Subu's relentless focus on hands-on engineering and building systems has pushed me to do things which I may not have thought about. Most of the dissertation stands on the collaborative work I have done with members across two laboratories at UCLA and it has been an absolute privilege. I would also be indebted to Prof. Rakesh Kumar at UIUC. Venturing into the realms of computer systems architecture research would not have been possible without him. He has been an ardent listener and a advisor and I have learnt many life lessons from him.

I would then like to thank all my internship mentors and collaborators. At Nvidia Corp., I worked under the guidance of Eiman Ebrahimi, Arslan Zulfiqar and David Nellans. The knowledge and insights from this internship immensely helped me with my research in systems architecture, in particular deep learning systems. Over the past two years since 2019, I have closely worked with Newsha Ardalani on developing DeepFlow and have learnt a lot over the course of the project.

She has been an excellent collaborator, friend and mentor. Thanks also to Qualcomm Innovation Fellowship for inviting me to present at Qualcomm Research (San Diego) in 2019 and 2020. I would also like to thank members of CDEN and CHIPS, who has provided very important feedback that has helped shape some of my research.

I would like to acknowledge the support of my lab mates: Dr. Mark Gottscho, Dr. Yasmine Badr, Dr. Shaodi Wang, Dr. Wei-Che Wang, Dr. Irina Alam, Tianmu Li, Wojciech Romaszkan, Shurui Li, Alexander Graening, SivaChandra Jangam, Krutikesh Sahoo, Steven Moran, and many from the CHIPS laboratory. I am thankful for their friendship and their inputs during technical discussions. I would also sincerely thank my collaborators form the PASSAT group at UIUC - Daniel Petrisko, Nicholas Cebry and Jingyang Liu. Particularly, I would thank Matthew Tomei with whom I have spent countless days and nights, brainstorming ideas, writing and debugging code and papers, and ofcourse pitching a startup company where we wanted to make novel waferscale systems. Finally, I will be forever grateful to Irina Alam for being my biggest support, friend and family here in LA in the past five years, for always inspiring and motivating me, and providing valuable inputs through lengthy discussions, and for proofreading all my papers.

Lastly and most importantly, I would like to thank my parents, Nupur Pal and Swapan Kumar Pal, and my brother Debapriya Pal for their unconditional love, unwavering support, and encouragement. I can never find enough words to express my gratitude towards them for their sacrifices and for the key role that they played in shaping my future. None of my accomplishments would have been possible without them.

# **Copyrights and Re-use of Published Material**

This dissertation contains significant material that has been previously published or is intended to be published in the future. Chapters 2 (Packageless Processors) contain material that were published in [9]. Chapter 3 includes material published in [10]. Chapter 4 (DSE for chiplet-assemmbly) appeared in [10]. Chapters 5 (Waferscale-GPU) appeared in [11] and 6 (Waferscale Design methodology) appeared in [12]. Chapter 7 (DL Multi-GPU Parallelism) includes material published in [13]. Chapter 8 (DeepFlow) is part of a paper which is under submission.

Some of the work in my PhD that was conducted in collaboration with other individuals (where I contributed, but did not lead) are not included in the body of this dissertation.

#### **VITA**

| 2015       | B.Tech., Indian Institute of Technology, Patna, India.                |

|------------|-----------------------------------------------------------------------|

| 2015       | Institute Silver Medal, Indian Institute of Technology, Patna, India. |

| 2015, 2019 | UCLA GuruKrupa Fellowship                                             |

| 2017       | M.S., Electrical Engineering, UCLA                                    |

| 2017       | Intel Best Student Paper Award, ECTC                                  |

| 2018       | PhD Intern, NVIDIA Corporation                                        |

| 2019       | Qualcomm Innovation Fellowship                                        |

| 2019       | Winner at EPFL Engineering PhD Summit on Intelligent Systems          |

| 2019       | Best Technical Presentation, UCLA ECE Annual Research Review          |

### **PUBLICATIONS**

**Saptadeep Pal**, Jingyang Liu, Irina Alam, Nicholas Cebry, Haris Suhail, Shi Bu, Subramanian S. Iyer, Sudhakar Pamarti, Rakesh Kumar, and Puneet Gupta. "Designing a 2048-Chiplet, 14336-Core Waferscale Processor." in *2021 58th ACM/IEEE Design Automation Conference (DAC)*, pp. 1183-1188.

**Saptadeep Pal**, Daniel Petrisko, Adeel A. Bajwa, Puneet Gupta, Subramanian S. Iyer and Rakesh Kumar, "A Case for Packageless Processors," in *2018 IEEE International Symposium on High* xxvi

Performance Computer Architecture (HPCA), Vienna, Austria, 2018, pp. 466-479.

**Saptadeep Pal**, Daniel Petrisko, Matthew Tomei, Puneet Gupta, Subramanian S. Iyer, and Rakesh Kumar, "Architecting waferscale processors-a GPU case study." in *2019 IEEE International Symposium on High Performance Computer Architecture (HPCA)*, pp. 250-263.

**Saptadeep Pal**, Irina Alam, Krutikesh Sahoo, Haris Suhail, Rakesh Kumar, Sudhakar Pamarti, Puneet Gupta, and Subramanian S. Iyer. "I/O Architecture, Substrate Design, and Bonding Process for a Heterogeneous Dielet-Assembly based Waferscale Processor." in *2021 IEEE 71st Electronic Components and Technology Conference (ECTC)*, pp. 298-303.

**Saptadeep Pal**, Daniel Petrisko, Rakesh Kumar, and Puneet Gupta. "Design space exploration for chiplet-assembly-based processors." *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* 28, no. 4 (2020): 1062-1073.

**Saptadeep Pal**, and Puneet Gupta. "Pathfinding for 2.5 D interconnect technologies." in 2020 ACM/IEEE International Workshop on System Level Interconnect Prediction (SLIP), pp. 1-8. IEEE, 2020.

**Saptadeep Pal**, Eiman Ebrahimi, Arslan Zulfiqar, Yaosheng Fu, Victor Zhang, Szymon Migacz, David Nellans, and Puneet Gupta. "Optimizing multi-GPU parallelization strategies for deep learning training." *IEEE Micro* 39, no. 5 (2019): 91-101.

SivaChandra Jangam, **Saptadeep Pal**, Adeel A. Bajwa, Sudhakar Pamarti, Puneet Gupta and Subramanian S. Iyer, "Latency, Bandwidth and Power Benefits of the SuperCHIPS Integration Scheme," in *2017 IEEE 67th Electronic Components and Technology Conference (ECTC)*, Orlando, FL, 2017, pp. 86-94.

# **CHAPTER 1**

## Introduction

Conventional computing is at a tipping point. On one hand, applications are fast emerging that have higher performance, bandwidth, and energy efficiency demands than ever before. On the other hand, the end of Dennard scaling as well as the slowdown of Moore's law diminishes the prospect of easy performance, bandwidth, or energy efficiency scaling in the future. Traditional framework of getting better performance and efficiency by developing and manufacturing large system-on-chips (SoCs) at the latest technology nodes is becoming prohibitively costly, more so for low- to medium-volume products. Moreover, fueled by the exponential growth of deep learning and big data analytics, scale-out systems composed of many SoCs are in great demand. Traditional integration technologies and methodologies of building scale-out systems, however, are failing to deliver the performance these applications demand. As a result of the above trends, future performance, power, and cost improvements cannot come from improvements in SoC technology alone. Then, how do we enable "System scaling"? To address this growing need, the research in this dissertation focuses on developing technology solutions and frameworks for system-technology co-optimization (STCO) which intersects the broad areas of computer architecture, VLSI design, and packaging. A novel system-level heterogeneous integration platform that enables packageless processing is introduced in Section 1.1. Section 1.2 briefly highlights the benefits of the novel chiplet-based waferscale processor architectures proposed and developed as part of the research in this dissertation. Section 1.3 then explains the importance of developing a cross-stack pathfinding frameworks for STCO. Overall, Scale-Out Packageless Processing provides a radically different dimension to system scaling and is described in Section 1.4 that summarizes all research projects covered in this dissertation.

# 1.1 A Novel Heterogeneous Integration Platform for Packageless Processing

Increasing SoC design and manufacturing cost in the latest technology processes is now making the industry look at alternative approaches to system design. An alternative approach, system-in-package (SiP), where multiple heterogeneous chiplets are integrated inside a package is gaining traction. SiP technologies, however, often lead to performance and/or energy efficiency overheads and are yet to deliver on their promise. Moreover, package-to-package links on printed circuit boards (PCBs) used to build integrated systems suffer from poor bandwidth, latency, and energy characteristics and often bottlenecks system performance. This is because of a striking observation that in the last two decades while silicon chips have dimensionally scaled by >1000X, package and PCB features have merely managed 5X. This absence of "system scaling" can severely limit the performance of processor systems. Though this realization has motivated the push toward 3D and 2.5D integration schemes, they however do not address the root cause.

This dissertation proposes a radically different approach – eliminating packages altogether and integrating all system components on a silicon board. To that end, we developed and prototyped a novel integration technology – Silicon Interconnect Fabric (Si-IF), as a potential replacement for PCB-based integration as the enabling technology for packageless processing. Si-IF technology allows integration of multiple bare silicon dies (chiplets) on a silicon substrate using very fine pitch copper pillar based I/O. The Si-IF is fabricated using a conventional and mature back end of line (BEOL) process which can have up to four levels of conventional copper dual damascene based interconnect. Si-IF allows I/O pitches to be less than 10  $\mu$ m and wire pitches to be as low as few hundred nanometers to a few microns. This enables us to build near on-chip-like parallel interfaces between chiplets. The custom designed area and energy-efficient I/O circuitry helps in delivering <0.1 pJ/bit energy efficiency of inter-chiplet communication on Si-IF. Besides, different chiplets can come from different technologies, for e.g. Si, GaN, InP, SiC etc. In fact, an SoC can be disintegrated and multiple component chiplets can now come from different technology nodes to optimize for cost and power. For e.g., a processor core can be in 32nm technology while L2 cache chiplet can be implemented in 22nm. Overall, Si-IF technology dramatically reduces the overhead of splitting an SoC into multiple chiplets and opens a foundational platform to minimize system

integration cost where hard-IPs, aka. chiplets can now be integrated to build a system without the penalties associated with conventional packaging.

The dissertation also proposes packageless processor architecture where we leveraged the unique properties of the Si-IF platform to (a) significantly improve memory bandwidth, which in turn helped us re-design the cache hierarchy, (b) improve thermal design power (TDP) by leveraging silicon's heat conduction properties for better cooling, and (c) increase processor core count by leveraging the area savings from removing packages. This improves processor performance by up to 3x while taking up 76% less area than its conventional counterpart. As human society becomes more reliant on computing and marches towards embedding computing in all facets of the physical world, packageless processing would help us achieve unprecedented performance and efficiency that cannot be delivered by today's technologies.

# 1.2 Chiplet-based Waferscale Processing

Today, the demand for parallel hardware is more than ever before. Waferscale processor systems can provide the large number of cores, and memory bandwidth and latency required by today's highly parallel workloads without the area and energy overhead incurred in conventional integration technologies. Older (1980s) and some recent works adopted waferscale integration to provide very large performance and energy efficiency gains compared to conventional systems. All these works, however, rely on monolithic waferscale integration. Monolithic waferscale chips are homogeneous and cannot integrate disparate technology such as dense memory needed for the next generation of data-intensive applications. Also, often they suffer from yield issues and must dedicate a sizeable number of resources for redundancy. This dissertation, for the first time, targets waferscale processing in a completely different way. Using the Si-IF technology, we can integrate a large number of heterogeneous known-good-chiplets on a full wafer-sized interconnect platform. This approach can help integrate TBs (instead of GBs) of memory (DRAM, Flash) alongside PFLOPs of compute (in the latest CMOS process) to target the most difficult problems in HPC and ML/AI.

A waferscale architectural design space is heavily influenced by different physical constraints such as thermal and power delivery. We show that using a waferscale GPU architecture. Our optimized

waferscale GPU architecture performs up to 19x better than an optimized scale-out GPU system using traditional packaging technologies. We also explored the design methodology challenges of building a chiplet-based waferscale system by attempting to design a 14,336-core shared memory waferscale prototype system. The scale of this prototype system forced us to rethink several aspects of the design flow such as power delivery and on-chip regulation methods, reliable waferscale clock distribution, waferscale fault-tolerant network design, chiplet and waferscale system test mechanisms, and multiple physical and architectural techniques to enhance system yield.

I believe that we are just at the beginning of a waferscale revolution. TSMC in 2020 announced a chiplet based waferscale integration platform, which Tesla has adopted for their Dojo supercomputer. Several new system architectures can be built with waferscale technologies which were earlier not possible because of the limitations of conventional technologies.

# 1.3 System-Technology Co-Optimization

Fueled by the AI revolution and exploding growth of warehouse-scale computing, the semiconductor industry is pouring in 10s of billions of dollars in developing new specialized architectures and systems tailored towards training and inference of large models and processing as well as building efficient cloud infrastructure. One countervailing trend is that migrating designs to cutting-edge processes do not always yield good returns on investment. Moreover, several promising candidate technologies (e.g., MRAM memory, CNT interconnects) and packaging and system solutions are being explored across the globe. Commercialization of these new technologies would need further large investments across the board. To aid with these investment decisions, the industry needs to understand the performance and energy impacts of these technologies across the design space of architectures and applications. This calls for rapid design space exploration and pathfinding frameworks which would allow us to quickly evaluate the effects of these new technologies on the end-to-end application-level performance. To that end, we co-developed and open-sourced one such tool, DeepFlow, for STCO targeted towards large-scale deep learning model training. Given the characteristics of the technology node (logic and SRAM density), packaging technology, system-level constraints such as area, power, etc., and the deep learning model graph, the tool can

rapidly explore the architectural search space and software parallelization strategies and outputs the best end-to-end training time.

#### 1.4 Dissertation Outline

The research in this dissertation focuses on developing and building novel technology solutions and system-technology co-optimization frameworks that provide a revolutionary new way of enabling the much-needed system scaling.

In Part 1, the three chapters highlight the bottlenecks of conventional packages and propose a novel heterogeneous integration platform that allows elimination of conventional packages and replaces PCB with a silicon based interconnection substrate i.e., Si-IF.

- Chapter 2 makes the case for packageless processors. Using a baseline packaged processor architecture, we show that removing the package and replacing the PCB with Si-IF could enable large gains in terms of performance coming from increased memory bandwidth, thermal design power (TDP) and area benefits.

- Chapter 3 focuses on comprehensively investigating silicon based 2.5D interconnects such as silicon interposer, EMIB and Si-IF. A pathfinding methodology for 2.5D interconnect technologies is developed and used to study inter-chiplet interconnect performance and energy as a function of dimensional and technology parameters.

- Chapter 4 presents an optimization framework for multi-system/chiplet based processor ecosystem. Multiple systems can be used to target a diverse set of applications where each system is used to run a subset of applications efficiently. Recent 2.5D integration based assembly techniques allow composing systems using multiple chiplets. Finding the smallest number of chiplets to build multiple systems is a problem which we also solve using our optimization framework.

In Part 2, the two chapters focus on analyzing and building chiplet-based waferscale systems using Si-IF technology where a large number of heterogeneous known-good-chiplets are integrated

on a full wafer-sized interconnect platform.

- Chapter 5 proposes a waferscale GPU architecture. It is shown that a waferscale architectural design space is heavily influenced by different physical constraints such as thermal and power delivery. Novel power delivery mechanisms and network design as well as cooling solutions are proposed to maximize the amount of compute and memory that can be reliably integrated on a wafer. Optimized waferscale-network topologies are discussed that help to balance the performance and yield of the substrate. Then, optimized thread scheduling and data placement techniques are designed for waferscale GPUs.

- Chapter 6 focuses on designing a 14,336-core shared memory waferscale prototype system. Several aspects of the design were built from the ground up due to the scale of the system: power delivery and on-chip regulation methods, reliable waferscale clock distribution, wafer-scale fault-tolerant network design, chiplet and waferscale system test mechanisms, and multiple physical and architectural techniques to enhance system yield. The chiplets were taped out in TSMC N40-LP node and a functional prototype was assembled in-house.

In Part 3, the two chapters focus on understanding the scalability characteristics of deep learning (DL) training applications and exploring the cross-stack impact of hardware-software-technology co-design at-scale.

- Chapter 7 studies which parallelization strategies to adopt to minimize end-to-end training time for a given DL model on available hardware. It is shown that hybrid parallelization (data parallelism[DP] and model parallelism[MP]) outperforms DP alone at different scales for different DL networks. An integer linear programming based tool is also developed to find optimal operation-to-device placement to maximize MP speedup.

- Chapter 8 explores the cross-stack impact of technology scaling, model scaling and architecture innovations from a holistic perspective, and at the same time considering real-world design constraints like area and power budget for deep learning training. Using this tool, we can perform rapid-yet-accurate design space exploration and find optimal architectures under given logic, memory, and inter-chip interconnect technology parameters.

Overall, the research in this dissertation focuses on system-technology co-optimization and provides a dramatically new dimension to system scaling. Such revolutionary new technology solutions and frameworks are absolutely needed to achieve performance, power and cost improvements in future systems as conventional technology scaling is becoming increasingly harder. The proposed chiplet-assembly based packageless processing and the scale-out waferscale architectures leveraging the novel integration technology developed in this dissertation provide the much needed performance and energy improvements for next-generation applications and are expected to create new areas of research.

# **CHAPTER 2**

# A Case for Packageless Processors

Demand for increasing performance is far outpacing the capability of traditional methods for performance scaling. Disruptive solutions are needed to advance beyond incremental improvements. Traditionally, processors reside inside packages to enable PCB-based integration. We argue that packages reduce the potential memory bandwidth of a processor by at least one order of magnitude, allowable thermal design power (TDP) by up to 70%, and area efficiency by a factor of 5 to 18. Further, silicon chips have scaled well while packages have not. We propose *packageless processors* - processors where packages have been removed and dies directly mounted on a silicon board using a novel integration technology, Silicon Interconnection Fabric (Si-IF). We show that Si-IF-based packageless processors outperform their packaged counterparts by up to 58% (16% average), 136% (103% average), and 295% (80% average) due to increased memory bandwidth, increased allowable TDP, and reduced area respectively. We also extend the concept of packageless processing to the entire processor and memory system, where the area footprint reduction was up to 76%.

#### 2.1 Introduction

Conventional computing is at a tipping point. On one hand, applications are fast emerging that have higher performance, bandwidth, and energy efficiency demands than ever before. On the other hand, the end of Dennard scaling [14] as well as Moore's law transistor scaling diminishes the prospect of easy performance, bandwidth, or energy efficiency scaling in future. Several promising and disruptive approaches are being explored, including (but not limited to) specialization [15], approximation [16], 3D integration [17], and non-CMOS devices [18].

Current systems place processor and memory dies inside packages, which allows them to be

connected to the PCB and subsequently to other dies. A striking observation is that in the last two decades while silicon chips have dimensionally scaled by 1000X, packages on printed circuit boards (PCBs) have merely managed 4X [19]. This absence of "system scaling" can severely limit performance of processor systems. This realization has motivated the push toward 3D and 2.5D integration schemes which alleviate the problem but do not address the root cause. In this work, we propose another approach - removing the package from the processor altogether.

At first glance, removing the package from the processor may seem both simple in implementation and, at best, incremental in benefits. However, neither is true. Packages significantly limit the number of supportable IOs in the processor due to the large size and pitch of the package-to-board connection relative to the size and pitch of on-chip interconnects ( $\sim 10X$  and not scaling well). In addition, the packages significantly increase the interconnect distance between the processor die and other dies. Eliminating the package, therefore, has the potential to increase bandwidth by at least an order of magnitude (Section 2.2). Similarly, processor packages are much bigger than the processor itself (5 to 18 times bigger). Removing the processor package frees up this area to either be used in form factor reduction or improving performance (through adding more computational or memory resources in the saved area). Lastly, packages limit efficient heat extraction from the processor. Eliminating the processor package can significantly increase the allowable thermal design power (TDP) of the processor (up to 70%). Increase in allowable TDP can be exploited to increase processor performance significantly (through frequency scaling or increasing the amount of computational or memory resources). Unfortunately, simply removing the processor package hurts rather than helps as we point out in Section 2.3. We develop a new silicon interconnect fabric to replace the PCB and make package removal viable in Section 2.4. Essentially, we place and bond bare silicon dies directly on to a silicon wafer using copper pillar-based I/O pins.

This chapter makes the following contributions:

- We make a case for packageless processors. We argue that modern processor packages greatly hinder performance, bandwidth, and energy efficiency scaling. Eliminating packages can enable us to recoup the lost performance, bandwidth, and energy efficiency.

- We present Si-IF, a novel integration technology, as a potential replacement for PCB-based

integration and as the enabling technology for packageless processing.