# MANUFACTURING ROADMAP FOR HETEROGENEOUS INTEGRATION AND ELECTRONICS PACKAGING (MRHIEP)

Final Report

# authorship

This roadmap addresses advanced packaging and was lead by UCLA CHIPS and SEMI (USA) and was sponsored by NIST under award 70NANB22H038, and is submitted as final report.

Principal Investigators: Subramanian Iyer (till September 2023) and Gity Samadi.

## Chapters

Acknowledgements

**Authors and Editors**

Glossary of terms

Chapter 1: MRHIEP Executive Summary

Chapter 2: Advanced Packaging & Heterogeneous Integration

Chapter 3: Medical/Hybrid Electronics

Chapter 4: Reliability and Thermal Challenges

Chapter 5: Modeling and Simulation

Chapter 6: Modular Chiplet Packaging for an Open Chiplet Economy

Chapter 7: Security in Heterogeneous Integration and Advanced Packaging

Chapter 8: Heterogeneous Integration Test Technology

Chapter 9: Advanced Packaging Supply Chain for High Performance Computing

Chapter 10: Smart Manufacturing Technology for Heterogeneous Integration & Advanced Packaging

Please select a chapter to continue reading.

# Acknowledgement

The MRHIEP organizing committee extends its heartfelt gratitude to the dedicated volunteers and their respective companies for their unwavering support and significant contributions to the success of the MRHIEP Package Roadmap effort. Your commitment and expertise have played a pivotal role in development of practical and sustainable roadmaps for key advanced packaging areas including materials, manufacturing process flows, cross-cutting technologies, chiplet architectures, simulations, electrical & mechanical standards, Supply Chain, Security, Test and Smart Manufacturing.

We also thank our executive committee: Akshay Singh (Micron), Tom Rucker (Intel), Melissa Grupen-Shemansky (SEMI), Gity Samadi (SEMI), Subu Iyer (UCLA CHIPS till September 2023), Om Nalamasu (AMAT), Eric Forsythe (US ARL) for providing constant and valuable guidance.

We also extend our gratitude to the members of previously established Technical Working Groups (TWG) in the Heterogeneous Integration Roadmap (HIR) for their pioneering efforts and the wealth of insights they provided throughout the road-mapping process. Your groundwork has paved the way for our current initiative, and we appreciate the valuable knowledge and experience you have shared.

We thank Hetal Jain (UCLA CHIPS) for administrative support.

The chapters developed through the MRHIEP efforts have aimed to identify the gaps in the existing advanced packaging infrastructure in the US with viable approaches to overcome these gaps. In addition, they provide targeted metrics to be achieved over the next 15 years for a sustainable advanced packaging ecosystem. We expect MRHIEP to shape the future of heterogeneous integration, chiplet ecosystem and advanced packaging. We look forward to continuing this collaborative journey as we shape the future of manufacturing, heterogeneous integration and electronics packaging together.

Sincerely,

Kouhkely Jaher

Krutikesh Sahoo (on behalf of Subramanian Iyer, UCLA CHIPS and Gity Samadi, SEMI) UCLA CHIPS Los Angeles, CA January 5, 2024

### **Authors:**

Abhijit Dasgupta (Univ of Maryland)

Anshu Bahadur (Deloitte)

Anu Ramamurthy (Microchip)

Arvind Kumar (IBM)

Bapi Vinnakota (ODSA)

Benson Chan (Binghamton)

Benjamin Fasano (Consultant)

Boris Vaisband (McGill) **Daniel Berger ( Consultant)**

Dave Armstrong (Advantest)

Dharmesh Jani (META)

Eric Forsythe (US Army Research Lab)

Gamal Refai Ahmed (AMD)

Gerald Pasdast (Intel)

Gity Samadi (SEMI)

Habib Hichri (Ajinomoto Fine Techno US)

Hanwen Chen (Applied Materials)

Harry Chen (MediaTek)

Ira Leventhal (Advantest)

Jeorge Hurtarte (Teradyne) Jerry McBride (Micron)

Jobert van Eisden (Atotech/MKS)

John Shalf (LBL)

Josh Dillon (Marvell)

Joy Watanabe (EMD Electronics)

Kanda Tapily (Tokyo Electron US)

(Names in Bold indicate section leads)

**Editors:**

Gity Samadi

Krutikesh Sahoo

Subramanian S. Iyer (until September 2023)

Venky Sundaram

Vineeth Harish

Kemal Aygun (Intel) Ken Butler (Advantest)

Ken Lanier (Teradyne)

Krutikesh Sahoo (UCLA CHIPS)

Lou Dadok (Fujifilm US)

Marc Hutner (Siemens)

Mark da Silva (SEMI)

Markus Leitgeb (AT&S)

Mary Ann Maher (SoftMems)

Michel Koopmans (Micron)

Morten Jensen (Intel)

Nader Sehatbakhsh (UCLA)

Naveed Hussain (AMAT)

Ram Kambhampati (Resonac US)

Reza Mahmoodian (Ulvac)

Rich Dumene (Renesas)

Robert Rodriquez (InnovaFlex Foundry)

Snehamay Sinha (Texas Instruments)

Steven Verhaverbeke (Applied Materials)

Subramanian S. Iyer (UCLA CHIPS) (till September 2023)

Tom Rucker (Intel)

**Venky Sundaram (Consultant)**

Vineeth Harish (UCLA CHIPS)

Wendy Chen (KYEC)

# Glossary of terms

| 3D IC Stacking                        | Techniques involving the integration of different<br>technologies and the stacking of multiple integrated<br>circuits (ICs) in three-dimensional configurations |  |  |  |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3D Printing                           | Additive manufacturing technique creating three-<br>dimensional objects layer by layer                                                                          |  |  |  |  |

| ADAS                                  | Advanced driver-assistance systems                                                                                                                              |  |  |  |  |

| Additive Manufacturing                | Manufacturing techniques that build objects layer by layer, adding material                                                                                     |  |  |  |  |

| Advanced Driver Assist Systems        | Vehicle safety systems that aid the driver in the                                                                                                               |  |  |  |  |

| (ADAS)                                | driving process                                                                                                                                                 |  |  |  |  |

| Advanced Packaging                    | New generation of packaging technologies such as 2                                                                                                              |  |  |  |  |

| Advanced Substrates                   | New generation of high-density substrates and                                                                                                                   |  |  |  |  |

|                                       | interposers, including silicon, glass and organic substrates, essential for advanced packaging                                                                  |  |  |  |  |

| AI (Artificial Intelligence)          | The simulation of human intelligence processes by                                                                                                               |  |  |  |  |

| , , , , , , , , , , , , , , , , , , , | machines, especially computer systems                                                                                                                           |  |  |  |  |

| AI-Driven Inspection                  | Inspection processes utilizing artificial intelligence                                                                                                          |  |  |  |  |

|                                       | algorithms and techniques for automated and precise                                                                                                             |  |  |  |  |

|                                       | quality control                                                                                                                                                 |  |  |  |  |

| AOA                                   | Angle of arrival                                                                                                                                                |  |  |  |  |

| AR/VR (Augmented                      | Technologies that create immersive, computer-                                                                                                                   |  |  |  |  |

| Reality/Virtual Reality)              | generated environments or enhance real-world                                                                                                                    |  |  |  |  |

|                                       | experiences through digital overlays                                                                                                                            |  |  |  |  |

| ASIC (Application-Specific            | A customized integrated circuit designed for a                                                                                                                  |  |  |  |  |

| Integrated Circuit)                   | specific purpose or application, often used in high-                                                                                                            |  |  |  |  |

|                                       | performance computing and specialized devices                                                                                                                   |  |  |  |  |

| ASP                                   | Average sales price                                                                                                                                             |  |  |  |  |

| ATE                                   | Automatic test equipment                                                                                                                                        |  |  |  |  |

| ATPG                                  | Automatic test pattern generation                                                                                                                               |  |  |  |  |

| Autonomous Driving                    | The ability of a vehicle to operate without human                                                                                                               |  |  |  |  |

|                                       | intervention, using sensors and software to navigate                                                                                                            |  |  |  |  |

|                                       | and control the vehicle                                                                                                                                         |  |  |  |  |

| AXI/CHI                               | Common bus protocols used in System-on-Chip                                                                                                                     |  |  |  |  |

|                                       | architectures                                                                                                                                                   |  |  |  |  |

| Backend Issues                        | Challenges related to chiplet integration that typically                                                                                                        |  |  |  |  |

|                                       | occur after the initial design phase, including                                                                                                                 |  |  |  |  |

| DEDÆ                                  | packaging, inventory management, and testing                                                                                                                    |  |  |  |  |

| BERT                                  | Bit-error-rate tester                                                                                                                                           |  |  |  |  |

| BGA                                   | Ball grid array                                                                                                                                                 |  |  |  |  |

| Biocompatibility                      | The ability of materials and substances to be                                                                                                                   |  |  |  |  |

|                                       | compatible with living tissues and biological systems                                                                                                           |  |  |  |  |

|                                       | without causing harm or rejection                                                                                                                               |  |  |  |  |

| BISC                                 | Built-in self-correlation/compensation                                                                                                                                                                                                      |  |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BISD                                 | Built-in self-diagnostics                                                                                                                                                                                                                   |  |  |  |  |  |

| BIST                                 | Built-in self-test                                                                                                                                                                                                                          |  |  |  |  |  |

| BOST                                 | Built-out self-test                                                                                                                                                                                                                         |  |  |  |  |  |

| BOW                                  | Bunch of wires                                                                                                                                                                                                                              |  |  |  |  |  |

| <b>Bumping and Assembly</b>          | Manufacturing processes involving the attachment of copper and/or solder bumps and assembly of                                                                                                                                              |  |  |  |  |  |

|                                      | electronic components onto substrates                                                                                                                                                                                                       |  |  |  |  |  |

| BW                                   | Bandwidth                                                                                                                                                                                                                                   |  |  |  |  |  |

| CAGR                                 | Compound annual growth rate                                                                                                                                                                                                                 |  |  |  |  |  |

| Capital Investments                  | Financial resources allocated for the development, manufacturing, and improvement of chiplet-based products, including investments in packaging technologies                                                                                |  |  |  |  |  |

| CCC                                  | Current carrying capacity                                                                                                                                                                                                                   |  |  |  |  |  |

| СНВ                                  | Copper hybrid bonding                                                                                                                                                                                                                       |  |  |  |  |  |

| Chiplet                              | Small, individual semiconductor components that<br>need to be integrated with other chiplets to create a<br>functional product, as opposed to monolithic devices<br>which are standalone integrated circuits                                |  |  |  |  |  |

| Co-Packaged Optics (CPO)             | Integration of optical components within electronic packaging for high-bandwidth and low-power data transmission                                                                                                                            |  |  |  |  |  |

| COT                                  | Cost of test                                                                                                                                                                                                                                |  |  |  |  |  |

| CPS                                  | Cyber-physical systems                                                                                                                                                                                                                      |  |  |  |  |  |

| CPU                                  | Central processing unit                                                                                                                                                                                                                     |  |  |  |  |  |

| CPU (Central Processing Unit)        | The primary component of a computer that performs most of the logic processing inside the computer                                                                                                                                          |  |  |  |  |  |

| Cu-Cu Hybrid Bonding                 | Bonding technique involving the use of direct copper-<br>to-copper bonding without solder, in combination with<br>oxide-to-oxide bonding to form ultra-fine pitch<br>interconnections, typically between two silicon chips<br>or substrates |  |  |  |  |  |

| D2D Interconnect and PHY             | Protocol and analog logic used to connect two chiplets in a package                                                                                                                                                                         |  |  |  |  |  |

| DARPA                                | Defense Advanced Research Projects Agency                                                                                                                                                                                                   |  |  |  |  |  |

| DDR                                  | Dual data rate (memory)                                                                                                                                                                                                                     |  |  |  |  |  |

|                                      |                                                                                                                                                                                                                                             |  |  |  |  |  |

| DFT                                  | Design for testability                                                                                                                                                                                                                      |  |  |  |  |  |

| DFT<br>DIB                           | Design for testability Device interface board                                                                                                                                                                                               |  |  |  |  |  |

| DFT                                  | Design for testability Device interface board Connections established between individual chiplets within a chip package, allowing them to communicate                                                                                       |  |  |  |  |  |

| DFT<br>DIB                           | Design for testability Device interface board Connections established between individual chiplets within a chip package, allowing them to communicate and work together                                                                     |  |  |  |  |  |

| DFT DIB Die-to-Die Interfaces        | Design for testability Device interface board Connections established between individual chiplets within a chip package, allowing them to communicate                                                                                       |  |  |  |  |  |

| DFT DIB Die-to-Die Interfaces Dielet | Design for testability Device interface board Connections established between individual chiplets within a chip package, allowing them to communicate and work together Hard instantiation of a chiplet design                              |  |  |  |  |  |

| DSP                            | Digital signal processing                                        |  |  |  |

|--------------------------------|------------------------------------------------------------------|--|--|--|

| DUT                            | Device under test                                                |  |  |  |

| DVFS                           | Dynamic voltage and frequency scaling                            |  |  |  |

| ECID                           | Electronic chip identifier                                       |  |  |  |

| EDA                            | Electronic design automation                                     |  |  |  |

| EIC                            | Electronic integrated circuit                                    |  |  |  |

| <b>Electrochemical Sensing</b> | Sensing technology based on chemical reactions                   |  |  |  |

| ě                              | involving electricity                                            |  |  |  |

| Electronics                    | Refers to components and systems involving                       |  |  |  |

|                                | electrical circuits and devices                                  |  |  |  |

| <b>Emerging Technologies</b>   | Novel and developing technologies that have the                  |  |  |  |

|                                | potential to significantly impact various industries and         |  |  |  |

|                                | everyday life                                                    |  |  |  |

| EPDA                           | Electronic/photonic design automation                            |  |  |  |

| EVM                            | Error vector magnitude                                           |  |  |  |

| Extreme Environmental          | Harsh or challenging environments that require                   |  |  |  |

| Conditions                     | specialized electronic components                                |  |  |  |

| Fan-Out Package                | Packaging technology where redistribution layers are             |  |  |  |

|                                | used to expand the on-chip IO area and enable direct             |  |  |  |

| FFT                            | board-level assembly of chips Fast Fourier transform             |  |  |  |

| Flexible Fanout Wafer Level    | Flexible packaging technique at the wafer level,                 |  |  |  |

| Packaging                      | enabling miniaturized hybrid electronic systems                  |  |  |  |

| Flexible Substrates            | Materials that can be bent and shaped without                    |  |  |  |

|                                | breaking, used in flexible electronics                           |  |  |  |

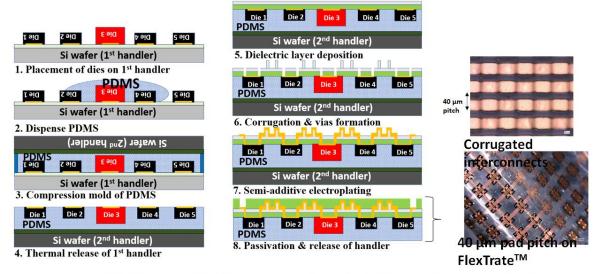

| Flextrate <sup>TM</sup>        | Die-first integration on flexible substrate followed by          |  |  |  |

|                                | molding and RDL buildup using wafer level                        |  |  |  |

|                                | processes.                                                       |  |  |  |

| Foundry Capacity               | The ability of semiconductor foundries to produce                |  |  |  |

|                                | chips in large quantities                                        |  |  |  |

| Front-end Device Manufacturing | The process of fabricating semiconductor devices on              |  |  |  |

|                                | the front-end of the production line                             |  |  |  |

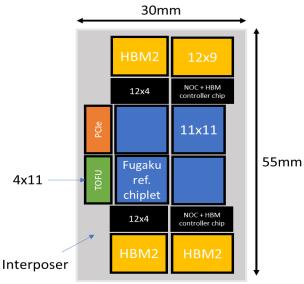

| Fugaku Supercomputer           | A high-performance supercomputer developed by                    |  |  |  |

|                                | RIKEN and Fujitsu, currently one of the fastest                  |  |  |  |

|                                | supercomputers in the world, used as a reference for             |  |  |  |

| GAN                            | deriving the modular architecture in the report  Gallium nitride |  |  |  |

| Gbps                           | Gigabits per second                                              |  |  |  |

| Geo-politics                   | The study of the effects of geography on international           |  |  |  |

| Geo-ponties                    | politics and international relations, specific to                |  |  |  |

|                                | semiconductor supply chains in this report                       |  |  |  |

| GPIO                           | General purpose input/output                                     |  |  |  |

| GPU                            | Graphics Processing Unit: A specialized electronic               |  |  |  |

|                                | circuit designed to accelerate the processing of images          |  |  |  |

|                                | the processing of manages                                        |  |  |  |

|                                | and videos in a computer                                         |  |  |  |

| Guardrails                        | Set boundaries or limitations within a modular                                |  |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| Guarurans                         | architecture, defining constraints such as die size,                          |  |  |  |  |  |

|                                   | bandwidth, thermals, and other attributes critical to the                     |  |  |  |  |  |

|                                   | final product's design and manufacture                                        |  |  |  |  |  |

| GUI                               | Graphical user interface                                                      |  |  |  |  |  |

| НВ                                | Hybrid Bonding                                                                |  |  |  |  |  |

| HBM                               | High bandwidth memory                                                         |  |  |  |  |  |

| HCI                               | Hot carrier injection                                                         |  |  |  |  |  |

| HDD                               | Hard disk drive                                                               |  |  |  |  |  |

| Heterogeneous Integration         | Combining different types of chiplets, each optimized                         |  |  |  |  |  |

| more ogeneous moegravion          | for specific tasks, within a single package to enhance                        |  |  |  |  |  |

|                                   | overall performance and functionality                                         |  |  |  |  |  |

| <b>High Performance Computing</b> | Computing systems that deliver high performance for                           |  |  |  |  |  |

| (HPC)                             | solving complex computational problems                                        |  |  |  |  |  |

| HIR                               | Abbreviation for the Heterogenous Integration                                 |  |  |  |  |  |

|                                   | Roadmap, a comprehensive technology roadmap for                               |  |  |  |  |  |

|                                   | the future of semiconductor devices, packages and                             |  |  |  |  |  |

|                                   | electronics systems                                                           |  |  |  |  |  |

| HSIO                              | High speed input/output                                                       |  |  |  |  |  |

| HVM                               | High-Volume Manufacturing, indicating large-scale                             |  |  |  |  |  |

|                                   | production of electronic components                                           |  |  |  |  |  |

| Hybrid Electronics                | Combining diverse technologies into a unified and                             |  |  |  |  |  |

|                                   | flexible substrate, enhancing the functionality of                            |  |  |  |  |  |

| TITAC                             | electronics used for medical and wearable applications                        |  |  |  |  |  |

| IJTAG                             | Internal Joint Test Action Group, refers to the IEEE 1687 family of standards |  |  |  |  |  |

| Interposer                        | A component used to connect semiconductor                                     |  |  |  |  |  |

| interposer                        | components within a package, typically at a level                             |  |  |  |  |  |

|                                   | between the chips and the package substrate                                   |  |  |  |  |  |

| IoT                               | Internet of Things, a network of interconnected                               |  |  |  |  |  |

|                                   | devices and objects exchanging data                                           |  |  |  |  |  |

| IP                                | Intellectual property                                                         |  |  |  |  |  |

| JTAG                              | Joint Test Action Group, refers to IEEE 1149 family                           |  |  |  |  |  |

|                                   | of standards                                                                  |  |  |  |  |  |

| KGD                               | Known good die                                                                |  |  |  |  |  |

| LBIST                             | Logic built-in self-test                                                      |  |  |  |  |  |

| LGA                               | Land grid array                                                               |  |  |  |  |  |

| LiDAR                             | Light Detection and Ranging, a remote sensing                                 |  |  |  |  |  |

|                                   | method using laser light for measuring distances                              |  |  |  |  |  |

| Lithography                       | The process of creating intricate patterns on surfaces                        |  |  |  |  |  |

|                                   | using light or radiation, a crucial step in                                   |  |  |  |  |  |

|                                   | manufacturing electronic components and packages                              |  |  |  |  |  |

| Low-cost Regions                  | Geographical areas with lower labor and production                            |  |  |  |  |  |

| MONA                              | costs, often targeted for outsourcing purposes                                |  |  |  |  |  |

| M2M                               | Machine-to-machine                                                            |  |  |  |  |  |

| Manufacturing Blueprint  | A detailed plan outlining generic process flows,<br>material and tool sets, and major suppliers for various                                                     |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Manufacturing Equipment  | packaging platforms  Machinery and tools used in the manufacturing                                                                                              |  |  |  |  |

| Manufacturing Equipment  | process of semiconductor devices                                                                                                                                |  |  |  |  |

| Materials & Chemicals    | Raw materials and chemicals used in the production of semiconductors                                                                                            |  |  |  |  |

| MBIST                    | Memory built-in self-test                                                                                                                                       |  |  |  |  |

| Memory                   | Electronic components used to store data and instructions temporarily or permanently in a computer system                                                       |  |  |  |  |

| Micro-fluidic Components | Miniaturized devices used for manipulating small amounts of fluids                                                                                              |  |  |  |  |

| MISR                     | Multiple input signature register                                                                                                                               |  |  |  |  |

| Modular Architecture     | A design approach where a system is divided into<br>smaller, manageable modules, allowing for flexibility,<br>scalability, and ease of integration              |  |  |  |  |

| Moore's Law              | The observation that the number of transistors on a microchip doubles approximately every two years, leading to increased computing power                       |  |  |  |  |

| MQTT                     | Message queueing telemetry transport                                                                                                                            |  |  |  |  |

| MRHIEP                   | Manufacturing Roadmap for Heterogenous<br>Integration and Electronics Packaging                                                                                 |  |  |  |  |

| MSE                      | Multi-site efficiency                                                                                                                                           |  |  |  |  |

| NBTI                     | Negative bias temperature instability                                                                                                                           |  |  |  |  |

| Noninvasive              | Procedures or devices that do not penetrate the body                                                                                                            |  |  |  |  |

| NRE                      | Non-recurring engineering                                                                                                                                       |  |  |  |  |

| OEE                      | Overall equipment efficiency                                                                                                                                    |  |  |  |  |

| Off-shoring              | The practice of relocating a business operation or process to another country                                                                                   |  |  |  |  |

| Onshore Supply Chain     | Manufacturing processes and resources located within the domestic boundaries of a country, ensuring self-sufficiency and reduced dependency on external sources |  |  |  |  |

| Onshoring                | The practice of bringing manufacturing operations and jobs back to the domestic country from overseas locations                                                 |  |  |  |  |

| OOK                      | On-off keying                                                                                                                                                   |  |  |  |  |

| Optical Sensing          | Sensing technology using light properties to measure various parameters                                                                                         |  |  |  |  |

| OSAT                     | Outsourced semiconductor assembly and test                                                                                                                      |  |  |  |  |

| OTA                      | Over the air                                                                                                                                                    |  |  |  |  |

| Outsourcing              | The practice of contracting out certain business functions or processes to external third-party vendors                                                         |  |  |  |  |

| Overlay A course ov               | Duagicion in aligning different levens on commonants                                                  |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Overlay Accuracy                  | Precision in aligning different layers or components during the manufacturing process, ensuring high  |  |  |  |  |

|                                   | density multi-layer RDL structures, or chip assemblies                                                |  |  |  |  |

| PAM4                              | Pulse amplitude modulation 4-level                                                                    |  |  |  |  |

|                                   | -                                                                                                     |  |  |  |  |

| Panel-Level Packaging (PLP)       | Fan-out packaging performed at the panel level, enabling cost reduction and larger package sizes than |  |  |  |  |

|                                   |                                                                                                       |  |  |  |  |

| PCB                               | wafer-level fanout packages Printed circuit board                                                     |  |  |  |  |

| PDK                               |                                                                                                       |  |  |  |  |

| Photonic Integrated Circuit (PIC) | Process design kit Integrated circuit technology for manipulating light in                            |  |  |  |  |

| Thotome integrated circuit (FIC)  | optical systems                                                                                       |  |  |  |  |

| Photonic IO                       | Optical interconnections between components related                                                   |  |  |  |  |

| 1 notonic 10                      | to data transmission and communication using light                                                    |  |  |  |  |

| Photonics                         | Technology related to the generation, transmission,                                                   |  |  |  |  |

| 1 Motorics                        | and manipulation of light                                                                             |  |  |  |  |

| PIC                               | Photonic integrated circuit                                                                           |  |  |  |  |

| PKG                               | Package or packaging                                                                                  |  |  |  |  |

| Plastronics                       | Technology combining plastic and electronic                                                           |  |  |  |  |

|                                   | components                                                                                            |  |  |  |  |

| Polarization Maintaining Fiber    | Optical fiber that maintains the polarization state of                                                |  |  |  |  |

| (PMF)                             | light, used in advanced optical systems                                                               |  |  |  |  |

| PoP                               | Package on Package, a stacking technique where one                                                    |  |  |  |  |

|                                   | chip package is placed on top of another                                                              |  |  |  |  |

| PRBS                              | Pseudo-random binary sequence                                                                         |  |  |  |  |

| PSS                               | Portable stimulus standard                                                                            |  |  |  |  |

| PTE                               | Parallel test efficiency                                                                              |  |  |  |  |

| PV                                | Photovoltaic                                                                                          |  |  |  |  |

| QAM                               | Quadrature amplitude modulation                                                                       |  |  |  |  |

| QED                               | Quick error detect                                                                                    |  |  |  |  |

| QFN                               | Quad flat no-lead package                                                                             |  |  |  |  |

| QFP                               | Quad flat pack                                                                                        |  |  |  |  |

| QPSK                              | Quadrature phase shift keying                                                                         |  |  |  |  |

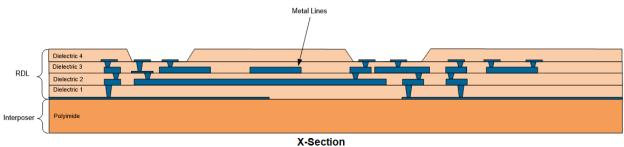

| RDL (Redistribution Layer)        | A layer of metal traces used to redistribute electrical                                               |  |  |  |  |

|                                   | connections on semiconductor devices and packages                                                     |  |  |  |  |

| RF                                | Radio frequency                                                                                       |  |  |  |  |

| RMA                               | Return material authorization                                                                         |  |  |  |  |

| Scale-down                        | The reduction in electrical and/or photonic IO pitch,                                                 |  |  |  |  |

|                                   | enabling increased channels per package and higher                                                    |  |  |  |  |

|                                   | bandwidth                                                                                             |  |  |  |  |

| Scale-out                         | Increasing system-level computing capacity by                                                         |  |  |  |  |

|                                   | adding more discrete units based on a massively                                                       |  |  |  |  |

|                                   | parallel architecture                                                                                 |  |  |  |  |

| Scaling                           | The ability to increase the performance, capacity, or                                                 |  |  |  |  |

|                                   | capabilities of a chiplet-based product, often                                                        |  |  |  |  |

|                          | accomplished by optimizing existing technology or                                                        |  |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

|                          | adopting new packaging methods                                                                           |  |  |  |  |

| SDC                      | Silent data corruption                                                                                   |  |  |  |  |

| SECS                     | Semiconductor equipment communications standard                                                          |  |  |  |  |

| SFDR                     | Spurious-free dynamic range                                                                              |  |  |  |  |

| SIC                      | Silicon carbide                                                                                          |  |  |  |  |

| Si-IF                    | Silicon Interconnect Fabric                                                                              |  |  |  |  |

| Single Mode Fiber (SMF)  | Optical fiber designed to carry a single light mode,                                                     |  |  |  |  |

| Single Wode Piber (SWIP) | used in high-speed data transmission                                                                     |  |  |  |  |

| SiP                      | System in Package, a packaging technology where                                                          |  |  |  |  |

|                          | multiple chips and passive components are integrated                                                     |  |  |  |  |

|                          | within a single package                                                                                  |  |  |  |  |

| SIP                      | System in package                                                                                        |  |  |  |  |

| SLT                      | System level test                                                                                        |  |  |  |  |

| SNR                      | Signal to noise ratio                                                                                    |  |  |  |  |

| SOC                      | System on chip                                                                                           |  |  |  |  |

| Soft Robotics            | Field of robotics dealing with soft and flexible robots                                                  |  |  |  |  |

| SOP                      | Small-outline package                                                                                    |  |  |  |  |

| SSD                      | Solid state drive                                                                                        |  |  |  |  |

| Standards                | Established guidelines and specifications that define                                                    |  |  |  |  |

|                          | various aspects of chiplet integration, including                                                        |  |  |  |  |

|                          | packaging, mechanical properties, thermal                                                                |  |  |  |  |

|                          | management, and power delivery, ensuring                                                                 |  |  |  |  |

|                          | compatibility and interoperability among different                                                       |  |  |  |  |

| OMP VI                   | vendors' products                                                                                        |  |  |  |  |

| STDF                     | Standard test data format                                                                                |  |  |  |  |

| SuperCHIPS               | Simple Universal Parallel intERface for CHIPS – high                                                     |  |  |  |  |

|                          | bandwidth, low power, low latency dielet-to-dielet                                                       |  |  |  |  |

| C                        | communication protocol.                                                                                  |  |  |  |  |

| Supply Chain Networks    | Interconnected systems of organizations, people,                                                         |  |  |  |  |

|                          | activities, information, and resources involved in the production and distribution of goods and services |  |  |  |  |

| Supply Chain Resiliency  | The ability of a supply chain to recover and adapt                                                       |  |  |  |  |

| Supply Chain Residency   | swiftly in the face of challenges, ensuring consistent                                                   |  |  |  |  |

|                          | production and delivery                                                                                  |  |  |  |  |

| Tailwinds                | Favorable external factors or trends that support a                                                      |  |  |  |  |

| A MAR VY RIEURY          | particular industry or business                                                                          |  |  |  |  |

| TAM                      | Test access mechanism                                                                                    |  |  |  |  |

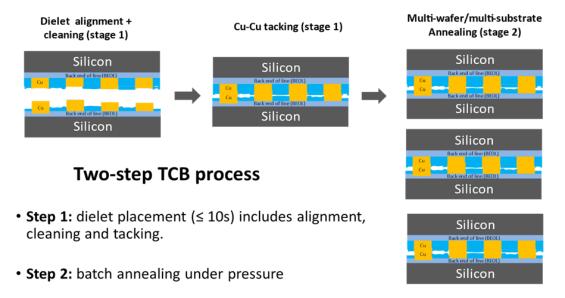

| TCB (Cu - Cu)            | Cu to Cu Thermal Compression Bonding without solder                                                      |  |  |  |  |

| TDDB                     | Time-dependent dielectric breakdown                                                                      |  |  |  |  |

| TDE                      | Touchdown efficiency                                                                                     |  |  |  |  |

| THD                      | Total harmonic distortion                                                                                |  |  |  |  |

| Thermal Dissipation      | The process of dissipating heat generated by                                                             |  |  |  |  |

|                          | electronic components to prevent overheating and                                                         |  |  |  |  |

|                          | ensure optimal performance                                                                               |  |  |  |  |

|                          | T T                                                                                                      |  |  |  |  |

| Thermal Management          | Techniques and technologies for controlling and optimizing the temperature of electronic devices and systems                                          |  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Throughput                  | The rate at which a process or system can complete tasks or transactions within a specific time frame, crucial for efficient manufacturing operations |  |  |  |  |

| TOF                         | Time of flight                                                                                                                                        |  |  |  |  |

| TSOP                        | Thin small-outline package                                                                                                                            |  |  |  |  |

| TSV                         | Through silicon via                                                                                                                                   |  |  |  |  |

| TSVs (Through-Silicon Vias) | Vertical conduits passing through a silicon wafer, enabling connections between stacked ICs                                                           |  |  |  |  |

| TTM                         | Time to market                                                                                                                                        |  |  |  |  |

| TWG                         | Abbreviation for Technical Working Group, focused on key identified areas                                                                             |  |  |  |  |

| TWR                         | Two way ranging                                                                                                                                       |  |  |  |  |

| UCIe, Bunch of Wires, XSR   | Standards for D2D interconnect                                                                                                                        |  |  |  |  |

| UPH                         | Units per hour                                                                                                                                        |  |  |  |  |

| UWB                         | Ultra wideband                                                                                                                                        |  |  |  |  |

| VCSEL                       | Vertical-cavity surface-emitting laser                                                                                                                |  |  |  |  |

| Wireless Power Transfer     | Technology enabling the transfer of power without physical connections                                                                                |  |  |  |  |

| WLCM                        | Wafer-level camera module                                                                                                                             |  |  |  |  |

| WLCSP                       | Wafer-level chip-scale packaging                                                                                                                      |  |  |  |  |

| WLO                         | Wafer-level optics                                                                                                                                    |  |  |  |  |

| WLP                         | Wafer-level packaging                                                                                                                                 |  |  |  |  |

# **Chapter 1: Report Summary**

### **Contents:**

| 1.1  | MRHIEP Goals and Organization                                         | 1              |

|------|-----------------------------------------------------------------------|----------------|

| 1.2  | MRHIEP Roadmap Challenges                                             | 2              |

| 1.3  | TWG1: Advanced Packaging Platforms                                    | 9              |

| 1.4  | TWG2: Cross-cutting Technologies                                      | 12             |

| 1.5  | TWG3: Chiplet Architectures and Standards                             | 12             |

| 1.6  | TWG4: Supply Chain, Security, Test and Smart Manufacturing            | 13             |

| 1.7  | Example of Manufacturing Gaps and Challenges: A Global Supply Chain I | Perspective on |

| Adva | anced Substrates                                                      | 14             |

### 1.1 MRHIEP Goals and Organization

The goal of MRHIEP is to develop an operational road map for jump starting advanced packaging in the US, with the creation of a quick-start guide for on-shore rapid development, piloting prototyping and manufacturing. This manufacturing roadmap is inspired by the Heterogeneous Integration Roadmap (HIR). MRHIEP focuses on leveraging on-shore skills, capabilities, and infrastructure, towards building on-shore resiliency with a diverse, robust, and secure global supply chain. MRHIEP is focused on defining a manufacturing-centric packaging roadmap for two major segments, (1) High performance computing (HPC) and (2) Medical electronics & hybrid device packaging. It is believed that these two sectors can provide a foundational developmental roadmap for other applications sectors such as rf/mm wave, automobile, and power electronics as well.

MRHIEP was organized into four technical working groups (TWGs) with major themes as shown below:

TWG1: Advanced Packaging Platforms

TWG2: Cross-cutting Technologies (Thermal, Reliability, Modeling and Simulation)

TWG3: Chiplet Architectures and Standards

TWG4: Supply Chain, Security, Test and Smart Manufacturing

The TWG members provided detailed input to the TWG leaders and this forms the basis of this report.

Additionally, the roadmap was validated by an industrial board of advisors. A three person steering committee from UCLA CHIPS and SEMI provided day-day operational guidance.

### 1.2 MRHIEP Roadmap Challenges

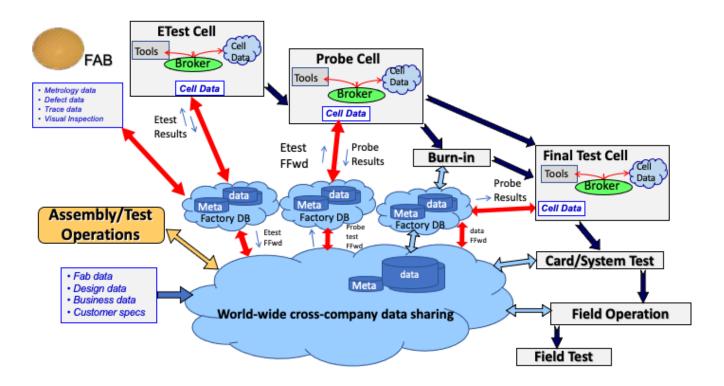

The roadmap challenges can be summarized as shown in Figure 1.1 and elements of each will be covered in the technical working group (TWG) summaries in this report.

Figure 1.1. MRHIEP Manufacturing Roadmap Challenges

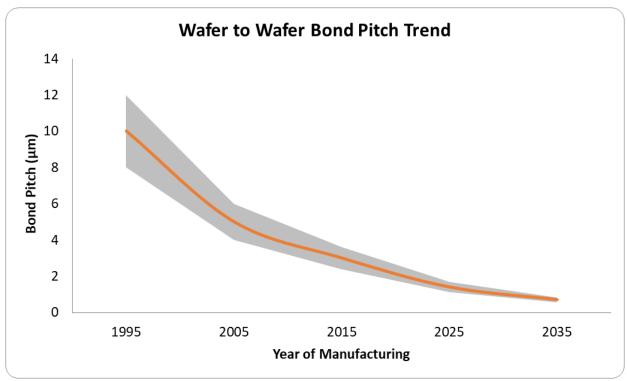

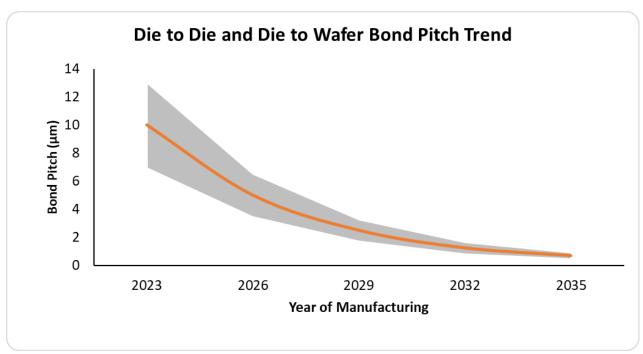

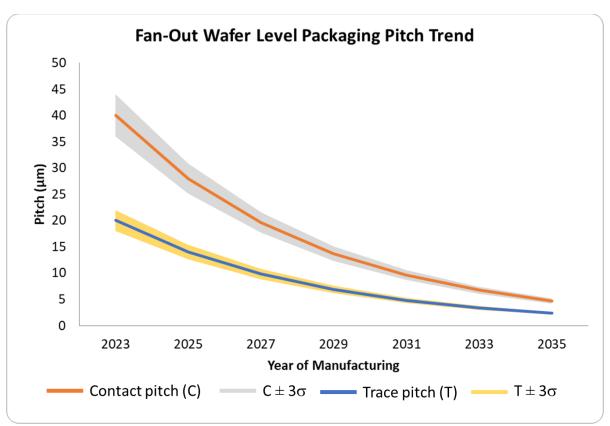

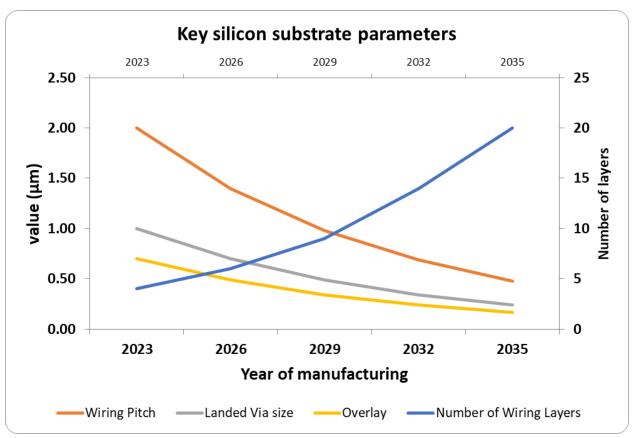

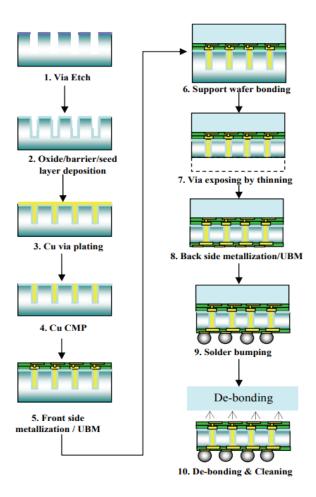

Several detailed roadmap charts were compiled by the MRHIEP team to represent the system-level roadmap requirements for high performance computing. These were translated to key advanced packaging metrics as shown below in Figure 1.2(a-f). These charts were extrapolated from the HIR roadmap to provide a more manufacturing-based visual of future trends until 2035. The same information is also provided in tabular form in Table 1.1 (a-f).

Table 1.1 (a) MRHIEP roadmap requirements for wafer-to-wafer bond pitch.

| year of manufacturing | -3σ (μm) | Nominal wafer-to-<br>wafer bond pitch (µm) | +3σ (μm) |

|-----------------------|----------|--------------------------------------------|----------|

| 1995                  | 8        | 10                                         | 12       |

| 2005                  | 4        | 5                                          | 6        |

| 2015                  | 2.4      | 3                                          | 3.6      |

| 2025                  | 1.12     | 1.4                                        | 1.68     |

| 2035                  | 0.56     | 0.7                                        | 0.84     |

Figure 1.2 (a) MRHIEP roadmap requirements for wafer-to-wafer bond pitch with  $\pm 3\sigma$ .

Table 1.1 (b) MRHIEP roadmap requirements for die-to-die and die-to-wafer bond pitch.

| Year of manufacturing | -3σ (μm) | Nominal die-to-die &<br>die-to-wafer bond<br>pitch (µm) | +3σ (μm) |

|-----------------------|----------|---------------------------------------------------------|----------|

| 2023                  | 7        | 10                                                      | 13       |

| 2026                  | 3.5      | 5                                                       | 6.5      |

| 2029                  | 1.75     | 2.5                                                     | 3.25     |

| 2032                  | 0.875    | 1.25                                                    | 1.625    |

| 2035                  | 0.49     | 0.7                                                     | 0.91     |

Figure 1.2 (b) MRHIEP roadmap requirements for die-to-die and die-to-wafer bond pitch with  $\pm$   $3\sigma$ .

Table 1.1 (c) MRHIEP roadmap requirements for fanout wafer level packaging (FOWLP) pitch.

| Year of manufacturing | Contact<br>pitch, C<br>(µm) | Trace<br>pitch, T<br>(µm) | C +3σ (μm) | C -3σ (μm) | T +3σ (μm) | Τ -3σ (μm) |

|-----------------------|-----------------------------|---------------------------|------------|------------|------------|------------|

| 2023                  | 40                          | 20                        | 44         | 36         | 22         | 18         |

| 2025                  | 28                          | 14                        | 30.8       | 25.2       | 15.4       | 12.6       |

| 2027                  | 19.6                        | 9.8                       | 21.56      | 17.64      | 10.78      | 8.82       |

| 2029                  | 13.72                       | 6.86                      | 15.09      | 12.34      | 7.54       | 6.17       |

| 2031                  | 9.60                        | 4.80                      | 10.56      | 8.64       | 5.28       | 4.32       |

| 2033                  | 6.72                        | 3.36                      | 7.39       | 6.05       | 3.69       | 3.02       |

| 2035                  | 4.70                        | 2.35                      | 5.17       | 4.23       | 2.58       | 2.11       |

Figure 1.2 (c) MRHIEP roadmap requirements for fanout wafer level packaging (FOWLP) contact and trace pitch with  $\pm 3\sigma$ .

Table 1.1 (d) MRHIEP roadmap requirements important silicon substrate parameters.

| Year of<br>Manufacturing | Number of<br>Wiring Layers | Wiring Pitch<br>(µm) | Landed Via size<br>(µm) | Overlay (µm) |

|--------------------------|----------------------------|----------------------|-------------------------|--------------|

| 2023                     | 4.00                       | 2.00                 | 1.00                    | 0.70         |

| 2026                     | 6.00                       | 1.40                 | 0.70                    | 0.49         |

| 2029                     | 9.00                       | 0.98                 | 0.49                    | 0.34         |

| 2032                     | 14.00                      | 0.69                 | 0.34                    | 0.24         |

| 2035                     | 20.00                      | 0.48                 | 0.24                    | 0.17         |

Figure 1.2 (d) MRHIEP roadmap requirements for important silicon substrate parameters such as substrate wiring pitch, via size and number of wiring layers.

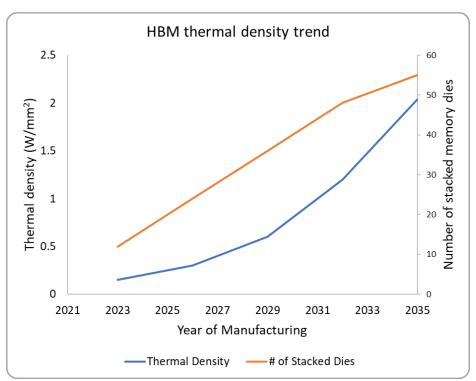

Table 1.1 (e) MRHIEP roadmap requirements for thermal density for high bandwidth memory.

| Year of Manufacturing | Thermal Density (W/mm²) | # of Stacked Dies |  |  |

|-----------------------|-------------------------|-------------------|--|--|

| 2023                  | 0.15                    | 12                |  |  |

| 2026                  | 0.3                     | 24                |  |  |

| 2029                  | 0.6                     | 36                |  |  |

| 2032                  | 1.2                     | 48                |  |  |

| 2035                  | 2.04                    | 55                |  |  |

Figure 1.2 (e) MRHIEP roadmap requirements for thermal density for high bandwidth memory.

Table 1.1 (f) MRHIEP roadmap requirements for thermal density for logic strata.

| Year of Manufacturing | Thermal Density (W/mm²) | # of Stacked logic strata |

|-----------------------|-------------------------|---------------------------|

| 2023                  | 1                       | 2                         |

| 2026                  | 2                       | 3                         |

| 2029                  | 3                       | 4                         |

| 2032                  | 4                       | 5                         |

| 2035                  | 5                       | 5                         |

Figure 1.2 (f) MRHIEP roadmap requirements for thermal density for logic strata.

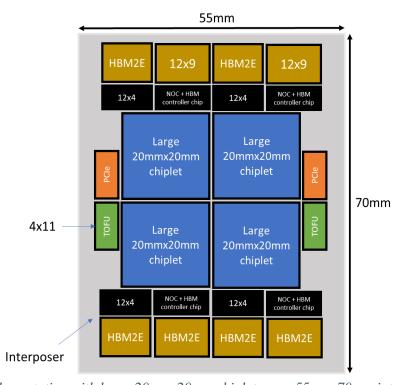

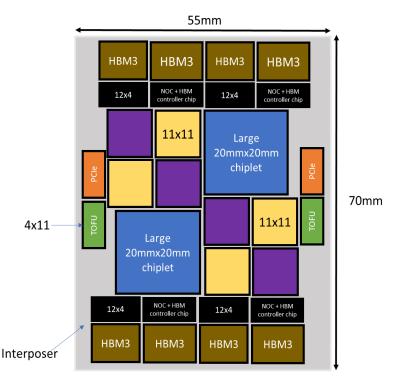

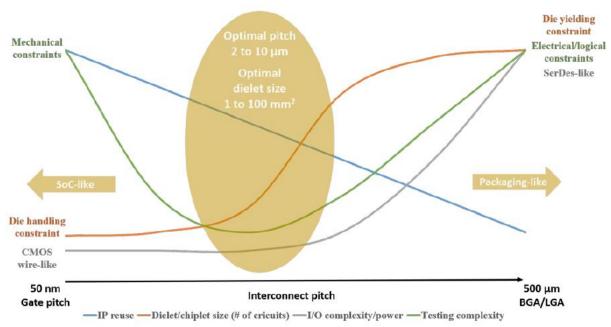

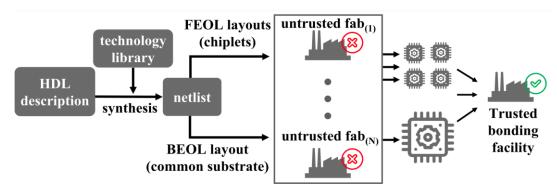

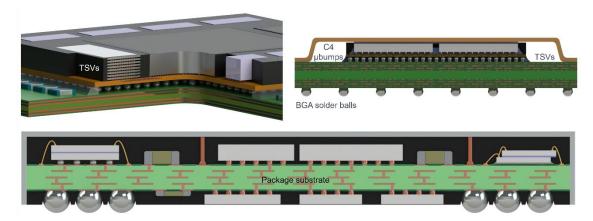

**High Performance Computing (HPC):** The roadmap specifies the scale-down and scale-out of packaging solutions that will integrate an ever increasing number of heterogeneous dielets to provide more functionality than can be provided by monolithic solutions alone, and, at lower cost, higher performance and lower power. Scale-down refers to the increase of channels per package through a steady reduction of all packaging dimensions. For example, bump pitches of today's advanced packaging will need to scale-down from ~30-50µm to approach the via pitches of onchip via numbers of 1um or even <1um pitches. Photonic I/Os will require decreases in fiber pitch to 80um and less with increasing fiber count from 4-8 fibers today to numbers approaching 100. The main goal of scaling-down pitches is to reduce area per IO, reduce energy /bit for communication across the system, and reduce latency. Scale-out refers to more intimately connected semiconductors (Si, III-Vs etc), and other functional elements (passives, sensors, energy storage) through an expanding use of chiplets/dielets (rather than large chips) that are architected to work together in a system of computation, uniform shared memory with "uniform and everything everywhere" connectivity. Heterogeneous Integration (HI) will require standards to allow for their reuse in an ever-increasing number of applications of these chiplet building blocks. These chiplets will need to be designed, modeled, and integrated within the application performance, reliability, thermal budget, cost, and system level link budget requirements with a special emphasis on dielet reuse. A chiplet warehousing strategy will need to be developed based on a chiplet discovery methodology. Chiplet designs will need to be widely available as bare dielets that can be integrated into user defined customizable assemblies with minimal design resources and a versatile automated design system. Assembly tool improvements to address combining "round" package elements and "square/rectangle" package elements will be needed for high volume manufacturing. These assembly tools and associated test methodologies with be a significant add to the existing packaging tooling available. Managing thermal dissipation will be in increasing focus as well, especially with the expansion of 3D stacking of dielets, closer dielet to dielet spacing (also to approach ~1um) and the use of a broad array chiplet types to include CPUs, GPUs, other domain specific compute engines, and diverse memory types and connectors (including photonics) that connect the packages to other packages and to the outside world. We

foresee an eventual radical departure from today's multi hierarchical packaging architecture to a simpler hierarchy, and the gradual limited use of interposers being replaced by the direct assembly of heterogeneous dielets on advanced substrates that exceed the connection densities of interposers and which also provide significant more functionality than interposers. These advanced substrates are essentially interconnecting fabrics based on silicon, (including heterogeneous semiconductors substrates such as Si, GaN on Si and high conductivity SiC). These silicon interconnect fabrics (Si-IFs) will have built-in passives, power delivery features and capability of both organic and inorganic buildup layers to extend their functionality. Furthermore, substrates based on glass cores with organic and inorganic build up layers and embedded active dies and passives as well as laterally composite substrates (also called compliant substrates) to allow for thermal expansion slack between rigid segments (similar to the rubberized fill between concrete slabs) are also possible for low power applications. For high performance applications, we see an eventual phasing out of organic cores and their replacement with semiconductor and glass cores each with multiple stress-balanced fine pitch wiring layers on both sides. We expect both sides of the substrate to be populated. We expect multiple substrates to be electrically or optically connected to further expand the electrical footprint of complex HPC systems.

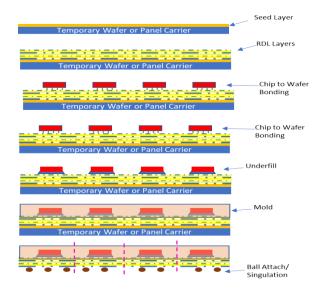

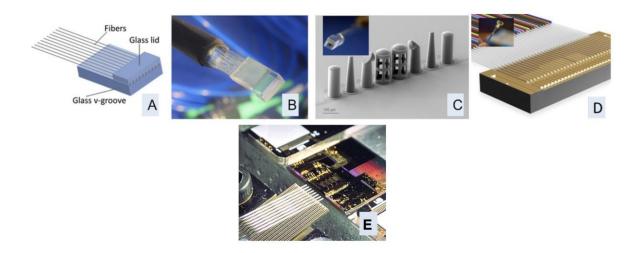

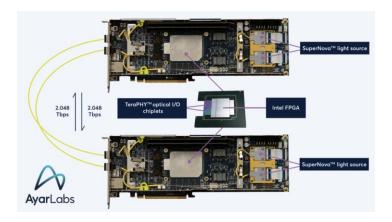

Another major driver of the HPC roadmap going forward is the expanding use of high speed connectors that may also include both rf/mm wave as well as co-packaged optics (CPO,) using new advanced packaging techniques. This is particularly important as AI data center and inter data center applications expand. Development needed to increase both wire and fiber density in these connectors with significant improvements in integration. Miniaturization and integration of rf/mm wave and photonic elements is a key to widespread adoption. The trade-off between bandwidth, bit error rate and power will be a major activity in the coming years with the emphasis being on reach, overall miniaturization (light source modulators, de-modulators and other electronics) cost and net power. We believe that wherever possible a wired solution will outperform a rf and photonics solution, though rf/mm wave solutions do present security vulnerabilities. Improvements in EDA systems to incorporate wired, rf/mm wave and photonic elements including their thermal environments will need to be made.

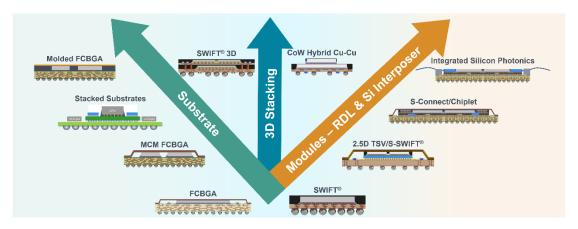

### 1.3 TWG1: Advanced Packaging Platforms

This technical working group consists of two sub-groups, focused on (a) High performance computing electronics, and (b) Medical and wearable hybrid electronics.

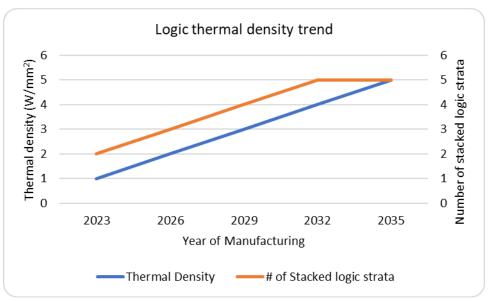

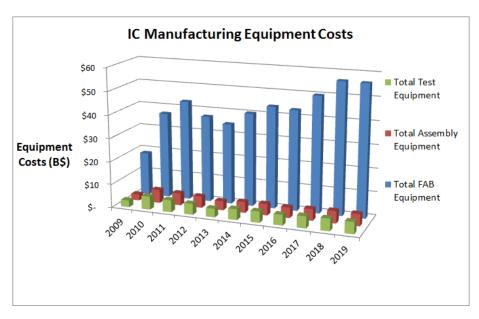

The Goal of TWG1 is to create a generic manufacturing roadmap and blueprint for manufacturing execution in key identified areas, building from HIR Roadmap and other relevant industry roadmaps. Advanced Packaging platforms have become critical to scaling electronic systems, yet a number of critical gaps exist in the onshore supply chain. The first edition of the manufacturing blueprint is focused on manufacturing gaps and potential solutions driven by the relevant technology roadmap chapters extracted from multiple editions of the HIR roadmap. The blueprint lays out detailed generic process flows with material and tool sets, as well as major suppliers (non-exhaustive) for each of the major packaging platforms. The working group has created 3-, 5- and 7-year targets and expanded on the onshoring gaps and solutions to create an actionable manufacturing roadmap. The major technology platforms included in the manufacturing blueprint with a focus on onshoring needs, are (a) Advanced Substrates, (b) Bumping and Assembly, (c) Hybrid Bonding and 3D IC stacking, and (d) Fan out packaging – wafer and panel level.

Key manufacturing roadmap gaps & challenges highlighted in this report are listed below.

- No advanced substrate manufacturing capability in the US.

- Equipment and material enablement gaps exist in all technology platforms to meet end user needs in a 3-10 year time frame.

- Onshore gaps exist in assembly and test at fine pitches.

- Power and thermal challenges in the roadmap need new solutions to support scaling.

- Hybrid electronics needs significant investments and additional focus inside HIR and other roadmaps.

The gaps and opportunities have been further sub-divided into two categories, namely,

- A. Leading-edge Gaps that Create Opportunities

- There is currently no high-volume, silicon-based package manufacturing infrastructure in the US.

- Die-to-Die interconnect pitch scaling roadmaps create new opportunities to address lithographic tools and process gaps for large area patterning.

- Bond pitch scaling with hybrid bonding and alternate assembly methods require innovations in plasma or other dicing, cleans and metrology steps to achieve high yields and cost-effective volume manufacturing.

- B. Supply Chain Resiliency Gaps

- The biggest gap in the onshore packaging supply chain for high performance computing is the lack of any advanced organic substrate manufacturing infrastructure in the US.

- Addressing the lack of non-captive, high volume bumping and assembly infrastructure in the US is another key to ensuring supply chain resiliency.

**Substrates/Interposers:** Wide-area lithography that can scale to sub-micron dimensions is a major gap in the global as well as onshore supply chains. The basis for this gap is the combination of reticle stitching & layer count escalation, resulting in worst case scenarios with >100 unique masks to build RDL for one interposer design. Although large area projection printing can scale to 2um today, there is concern whether this platform can be extended to sub-micron pitches, while maintaining large image field areas. Direct write lithography has emerged in recent years as a viable alternative. However, concerns remain about the ability to achieve high throughput, high overlay accuracy, and high resolution, as package sizes increase beyond 100mm x 100mm and substrate warpage increases. Other major needs in substrates and interposers include metrology and electrical test methods and tools for yield management. The emergence of automated AI driven inspection has been identified as a promising direction for future substrates and interposers. Passive integration for power delivery efficiency will continue to be adopted in wafer and panel formats and further material as well as process innovations are necessary. Advances in GaN on Si and SiC substrates offer the ability to revolutionize power delivery making highly segmented, multi-domain efficient power delivery a reality within the next few years.

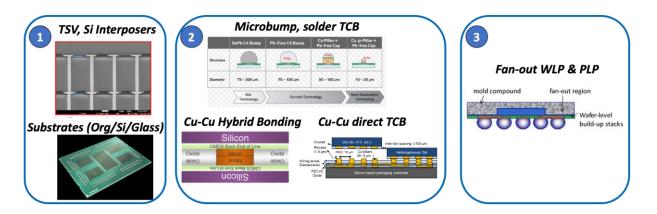

**Bond Pitch Scaling & Assembly:** Manufacturing challenges and gaps exist in increasing throughput for Cu-Cu hybrid bonding(HB) and direct thermo-compression bonding)TCB) (die to substrate) as bond pitches scale to below 10 microns. Key challenges for HB lie in process

tolerance, wafer reconstitution and shear strength especially at high connection densities. New methods such as plasma dicing and cleans to eliminate particle contamination will need to be introduced as hybrid bonding scales to high volume manufacturing. While TCB is more forgiving from a process tolerance perspective, TCB equipment needs significant improvement from an automation and alignment perspective. Continued focus needs to be placed on improved handling methods for thinner die with through semiconductor/substrate vias (TSVs). Another challenge will be on reducing the die to die spacing for use in assembly of die to wafer, or collective die to wafer integration techniques. Lastly, Wafer-scale RDL lithography and cross die topography management will be another manufacturing gap as bond pitch scales.

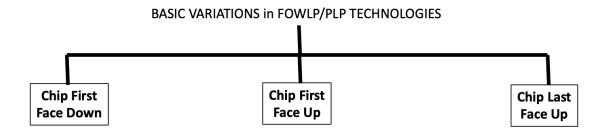

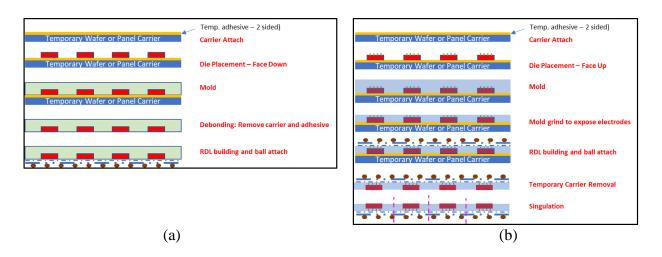

**Fan-out WLP/PLP:** Managing die shift and warpage as well as overlay accuracy are the major concerns in scaling the IO pitch for fanout packages. Better materials are needed for improved thermal dissipation as power density increases. The large area lithography challenge identified for substrates and interposers is even more critical to scale bond pitches for panel-level fanout packages (PLP). Recent innovations in carrier bonding and debonding will need to continue to progress to achieve the target process yields. Fanout approaches may also be used to build laterally heterogeneous substrates (including organic and glass core) to allow for accommodation of thermal expansion. This combined with AI mediated direct write lithography will allow for finer overall features over large areas enabling scale-down and scale-out.

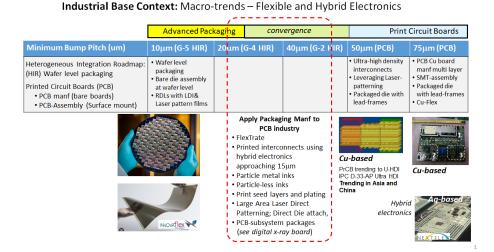

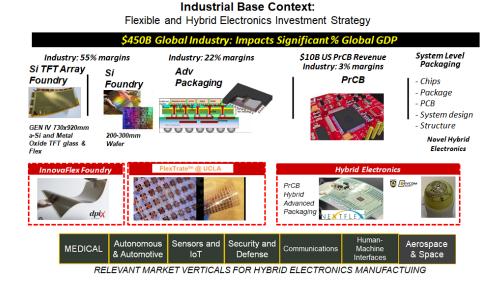

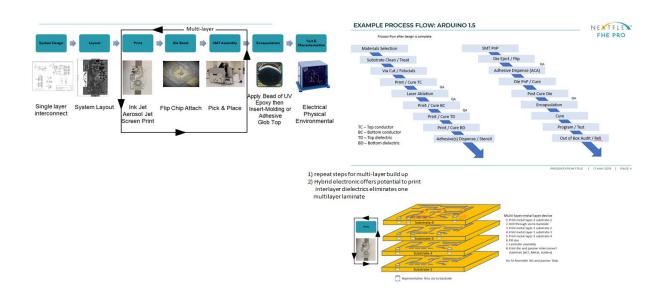

Medical/Hybrid Electronics: For medical/hybrid device packaging, increasing utilization and extension of flexible substrates through materials development and tooling to allow for broader technology application space that will include, asset monitoring such as electronics integrated onto large 3D-surfaces, communications arrays and associated electronics, soft robotics, electronics for extreme environmental conditions, to name a few. Medical applications are extensive and ensuring extreme flexibility, wireless power transfer, ultra-thin components below 100um in thickness and the incorporation of micro-fluidic components are all development extensions needed. The roadmap addresses increasing miniaturization, lower power consumption and energy production/harvesting, increasing accuracy, increasing connectivity with improvement in shape, flexibility, and conformance improvements for wearability. Packages will need to drive toward being noninvasive skin wearable with shifts from electrochemical toward improved optical sensing. Significant development and manufacturing investments will need to be focused towards 3D printing and other additive manufacturing methods.

The major challenges and opportunities in this area are summarized below.

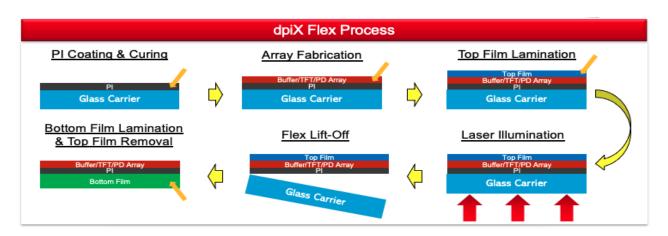

- Hybrid Integration combining various technologies into flexible substrates is of high interest to medical and wearable applications.

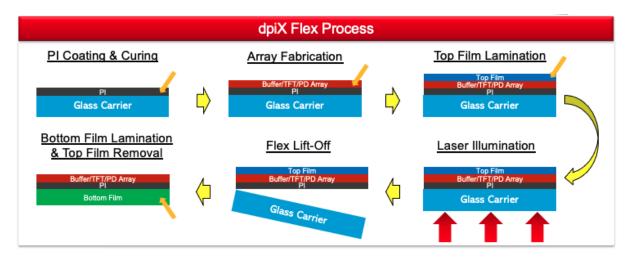

- Panel-level packaging is a major focus area for hybrid electronics, leveraging flexible display manufacturing infrastructure (e.g. DPiX).