### UNIVERSITY OF CALIFORNIA

Los Angeles

An on-chip ESD sensor for use in advanced packaging

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Kannan Kalappurakal Thankappan

© Copyright by

Kannan Kalappurakal Thankappan

2021

### ABSTRACT OF THE DISSERTATION

An on-chip ESD sensor for use in advanced packaging

by

Kannan Kalappurakal Thankappan

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Los Angeles, 2021

Professor Subramanian S. Iyer, Chair

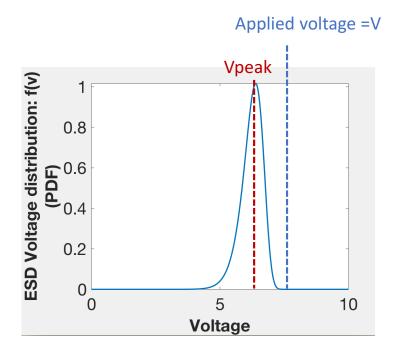

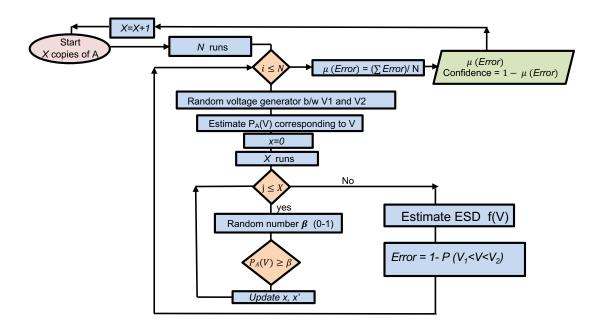

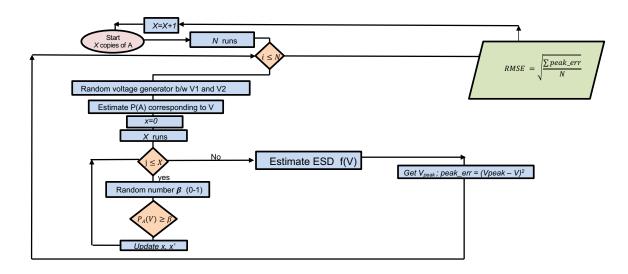

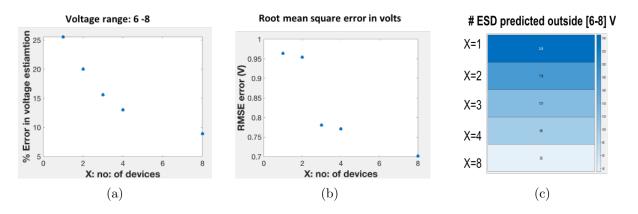

Electrostatic discharge (ESD) in integrated circuits (ICs) occurs due to charge transfer between two components in close proximity with voltage imbalance. As a result of an ESD event, a high transient current (up to few tens of Amps) and large voltage (up to several tens of kV) can develop between the two components. This fast ( $\sim 150 \, ns$ ) transient phenomenon can cause serious damage or degrade the performance of affected ICs. ESD results in about 35% of IC field returns and is the cause of several billion dollars loss to the semiconductor industry per year. Even though most modern ICs have on-chip ESD protection circuitry embedded, static charge accumulation during transport and handling may exceed the limits of ESD protection and cause damage to the ICs. Advanced packaging schemes existing today are not amenable to rework if one or more dielets are ESD compromised. An on-chip ESD sensor would help in identifying and preventing the assembly of ESD compromised dielets in any advanced packaging schemes. In this dissertation, two approaches for on-chip ESD detection that can be employed on any die are presented: variable dielectric width capacitor, and vertical MOSCAP array. The variable dielectric width capacitor approach employs metal plates terminated with sharp corners to enhance local electric field and facilitate easy breakdown of the thin dielectric between the metal plates. The vertical MOSCAP array consists of a capacitor array connected in series. Both approaches were designed, simulated, fabricated, and experimentally characterized on GlobalFoundries 22 nm fully depleted silicon-oninsulator (FDSOI) technology. The designed vertical MOSCAP arrays were able to detect ESD events  $\geq$  6 V while the variable dielectric width capacitor based sensor is able to detect ESD voltages  $\geq$  40 V. A Bayesian method was formulated for the estimation of ESD voltage using the sensors and experimentally validated. Mathematical formulation for sensitivity and confidence in ESD voltage estimation was developed which matches the results of Monte-Carlo simulations. A sensitivity of 1 parts per million is achievable with 4 sensors for an ESD voltage detection of 7.4 V. The simulation study further indicates that the error in voltage estimation can be reduced from 25% to 8% by increasing the number of sensors from 1 to 8.

Finally, a novel high-power delivery network for the Silicon interconnect fabric (Si-IF), a heterogeneous wafer-scale integration platform, is also proposed. The system is capable of 42 kW output power delivery to dielets when supplied with a 50-kW input power. Power delivery network (PDN) modelling and simulations have been carried out to determine impedance spectrum and  $I^2R$  losses. A 100 W experimental prototype was designed and evaluated to check the feasibility of the proposed architecture.

The dissertation of Kannan Kalappurakal Thankappan is approved.

Dwight Streit

Chee Wei Wong

Ali Mosleh

Subramanian S. Iyer, Committee Chair

University of California, Los Angeles 2021

To my mother

# Contents

| $\mathbf{C}$ | Contents |                                                       |      |  |

|--------------|----------|-------------------------------------------------------|------|--|

| Li           | st of    | Figures                                               | viii |  |

| Li           | st of    | Tables                                                | xi   |  |

| 1            |          | roduction                                             | 1    |  |

|              | 1.1      | Electrostatic discharge                               | 1    |  |

|              | 1.2      | ESD in advanced packaging                             | 20   |  |

|              | 1.3      | Organization of this Dissertation                     | 22   |  |

| 2            | ESI      | O susceptibility in Silicon-Interconnect fabric       | 23   |  |

|              | 2.1      | Silicon-Interconnect Fabric                           | 23   |  |

|              | 2.2      | Impact of employing ESD protection in Si-IF           | 25   |  |

|              | 2.3      | Si-IF assembly process and experimental setup         | 26   |  |

|              | 2.4      | Experimental results and discussion                   | 28   |  |

|              | 2.5      | Conclusions                                           | 31   |  |

| 3            | On-      | chip ESD monitor                                      | 32   |  |

|              | 3.1      | Introduction                                          | 32   |  |

|              | 3.2      | Variable dielectric width capacitor                   | 33   |  |

|              | 3.3      | Vertical MOSCAP Array                                 | 49   |  |

|              | 3.4      | Theoretical Analysis of the ESD Sensor                | 55   |  |

|              | 3.5      | Conclusions                                           | 57   |  |

| 4            | ESI      | O voltage estimation using sensors                    | 59   |  |

|              | 4.1      | Introduction                                          | 59   |  |

|              | 4.2      | Problem statement and Bayesian method formulation     | 60   |  |

|              | 4.3      | ESD testing of the sensors                            | 67   |  |

|              | 4.4      | Applied ESD voltage prediction from observed evidence | 71   |  |

|              | 4.5      | Sensitivity Of ESD Sensors                            | 78   |  |

|              | 4.6      | Confidence Measurement in ESD Voltage Estimation      | 81   |  |

|              | 4.7   | Conclusions                               | 89  |

|--------------|-------|-------------------------------------------|-----|

| 5            | Con   | clusion                                   | 90  |

|              | 5.1   | Summary                                   | 90  |

|              | 5.2   | Outlook                                   | 91  |

| $\mathbf{A}$ | Hig   | h-power delivery architecture for Si-IF   | 92  |

|              | A.1   | Introduction                              | 92  |

|              | A.2   | Power delivery network in Si-IF           | 95  |

|              | A.3   | Construction of power boards              | 100 |

|              | A.4   | Experimental results for prototype boards | 105 |

|              | A.5   | Conclusions and Future work               | 108 |

| Bi           | bliog | graphy                                    | 110 |

# List of Figures

| ESD damage in ICs                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Charged human body and floating device                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Charged human body and grounded device                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ESD models                                                                  | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Types of ionizers                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Over-head, bench top, and gun ionizers                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ESD prevention methodologies in workplace                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

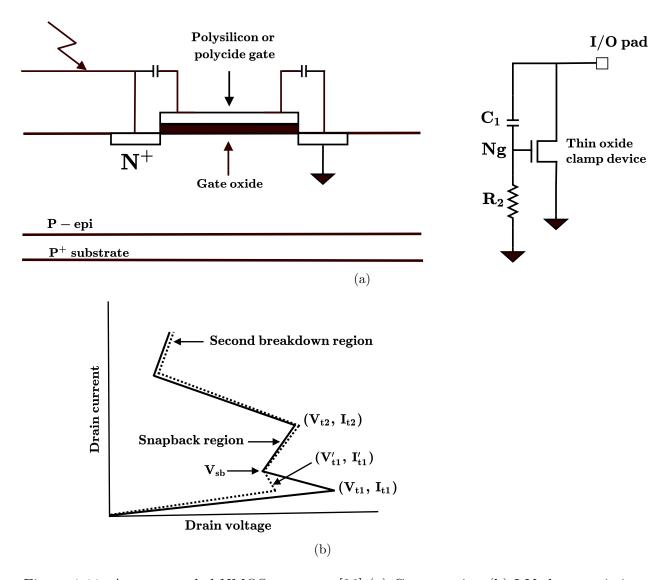

| A grounded gate NMOS ESD protection                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

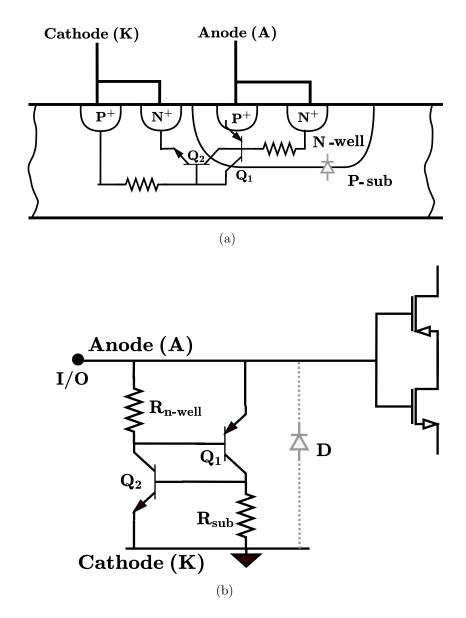

| SCR ESD protection                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A gate coupled NMOS structure                                               | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

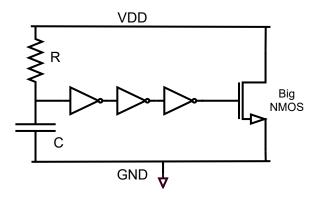

| NMOS ESD power clamp                                                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

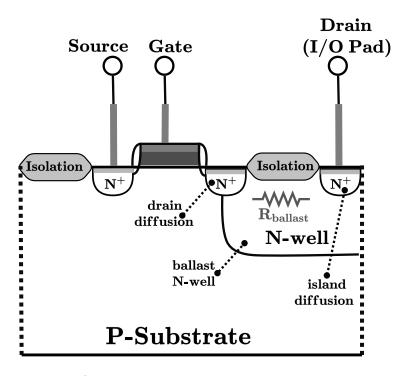

| Ballasting in multi-finger NMOS                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

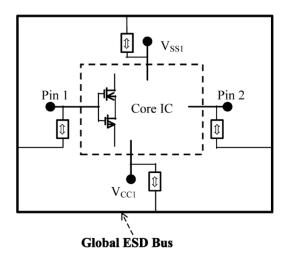

| Complete ESD protection                                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

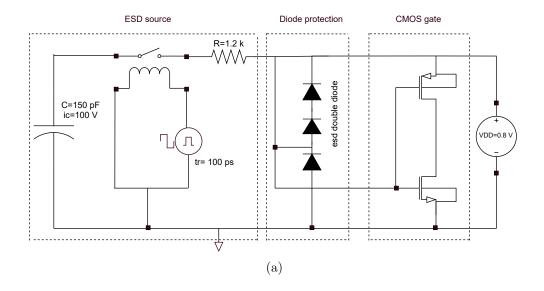

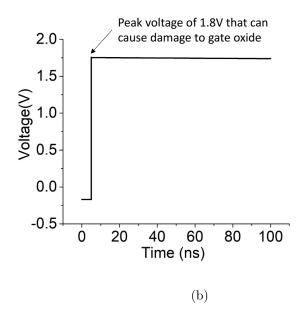

| ESD protection to a CMOS gate                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

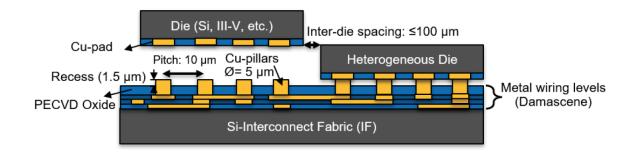

| Schematic of fine pitch assembly on Si-IF                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Dies integrated on a 100 mm Si-IF                                           | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

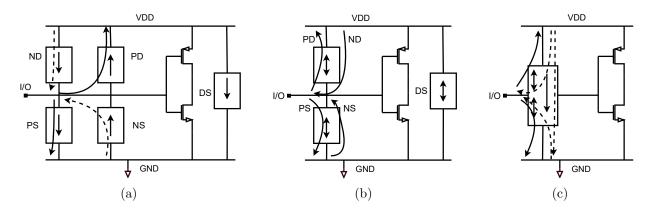

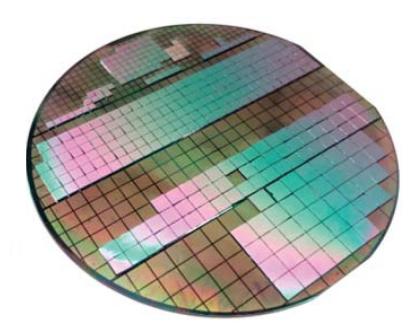

| Schematic of transceiver circuit without and with ESD protection            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

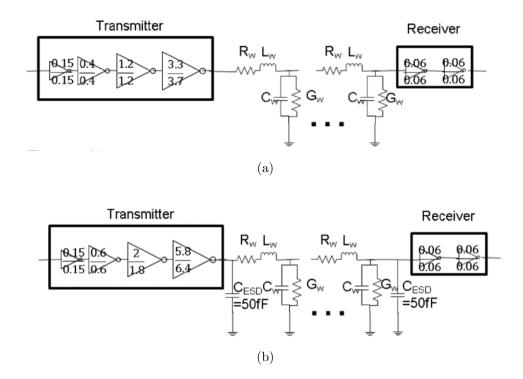

| Cross-sectional image of dielet and Si-IF in the assembly process           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

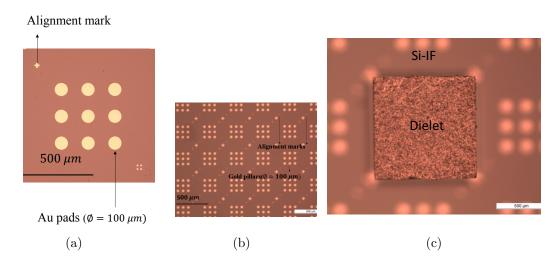

| Top view of dielet, Si-IF and a dielet bonded to Si-IF                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

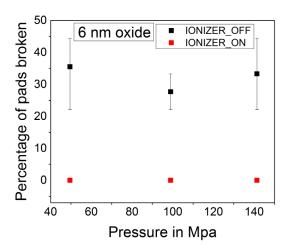

| ESD effect on dielet breakdown with ionizer off and on                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

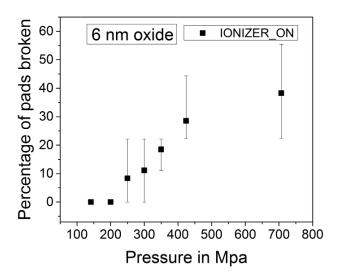

| Effect of pressure on dielet breakdown                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

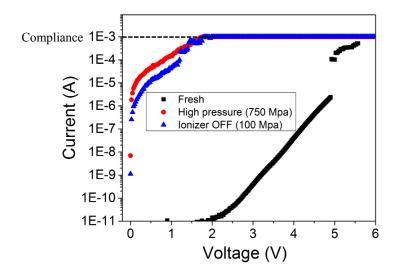

| I-V characteristics of broken down dielets by different mechanisms          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

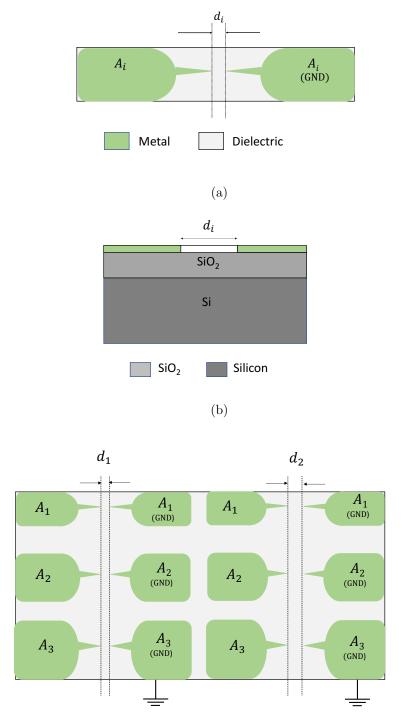

| Metal plates terminated with sharp corners separated by a thin dielectric 3 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

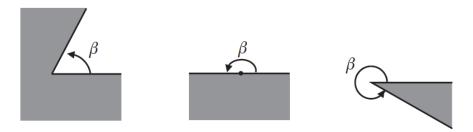

|                                                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

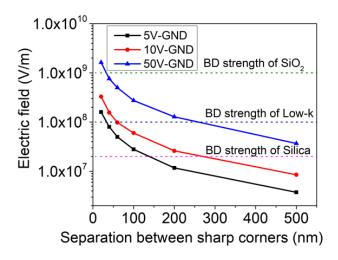

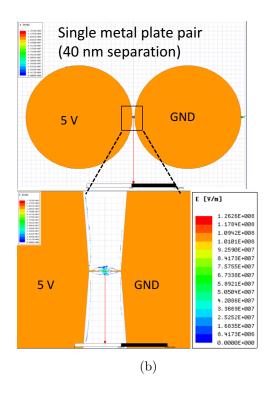

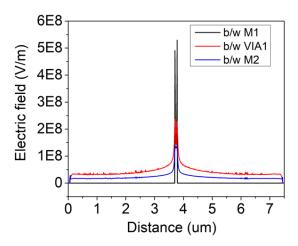

| Electric field profile between sharp corners                                | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             | Charged human body and floating device Charged human body and grounded device ESD models Types of ionizers 1: Over-head, bench top, and gun ionizers 1: ESD prevention methodologies in workplace 1: ESD protection 1: A grounded gate NMOS ESD protection 3: CR ESD protection 4 gate coupled NMOS structure 1: NMOS ESD power clamp 1: Ballasting in multi-finger NMOS 1: ESD global bus 1: ESD protection to a CMOS gate 2: Schematic of fine pitch assembly on Si-IF Dies integrated on a 100 mm Si-IF Schematic of transceiver circuit without and with ESD protection 2: Cross-sectional image of dielet and Si-IF in the assembly process 2: Top view of dielet, Si-IF and a dielet bonded to Si-IF ESD effect on dielet breakdown with ionizer off and on 2: Effect of pressure on dielet breakdown 1-V characteristics of broken down dielets by different mechanisms 3: Metal plates terminated with sharp corners separated by a thin dielectric Working principle of the ESD sensor unit Side view of a two-dimensional wedge 3: Electric field profile between sharp corners 3: CDM Test setup |

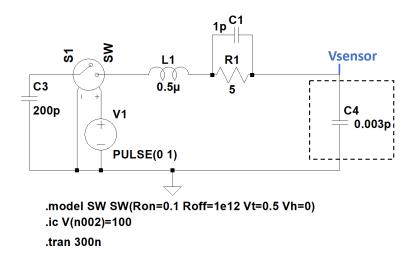

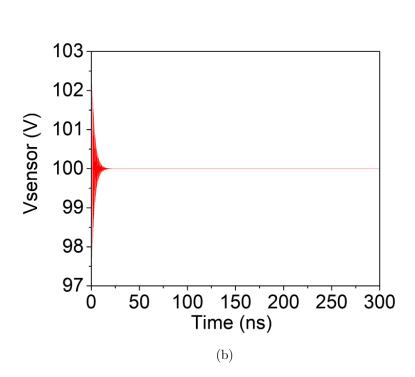

| 3.7          | CDM simulation                                                                                                                                           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.8          | HBM simulation                                                                                                                                           |

| 3.9          | MM simulation                                                                                                                                            |

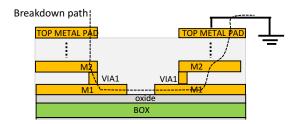

| 3.10         | Cross-sectional view of variable dielectric width capacitor                                                                                              |

| 3.11         | Electric field lines between metal plates for variable dielectric width capacitor .                                                                      |

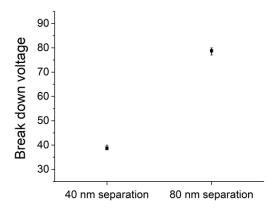

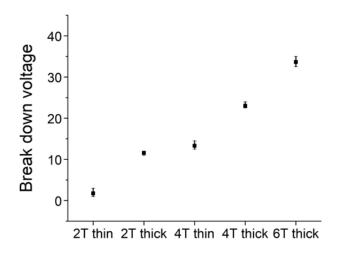

| 3.12         | Experimentally determined breakdown voltage characteristics of the variable di-                                                                          |

|              | electric width capacitor                                                                                                                                 |

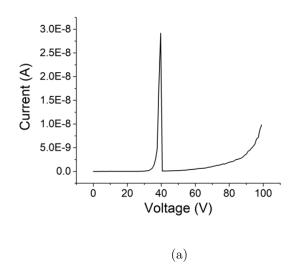

| 3.13         | Experimental I-V Characteristics of the variable dielectric width capacitor                                                                              |

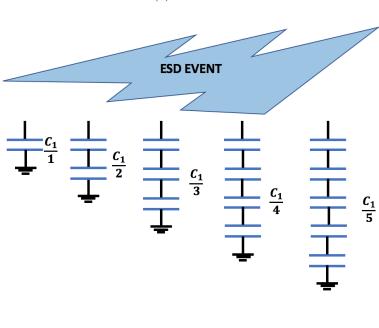

| 3.14         | Working principle of a vertical MOSCAP array                                                                                                             |

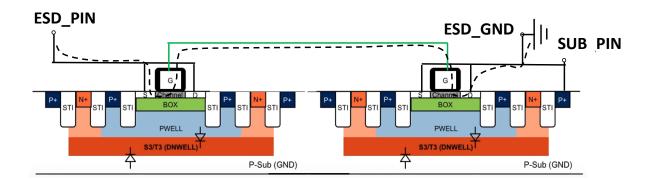

|              | Cross-sectional view of a two transistor vertical MOSCAP array in GF $22 \ nm$                                                                           |

|              | FDSOI technology                                                                                                                                         |

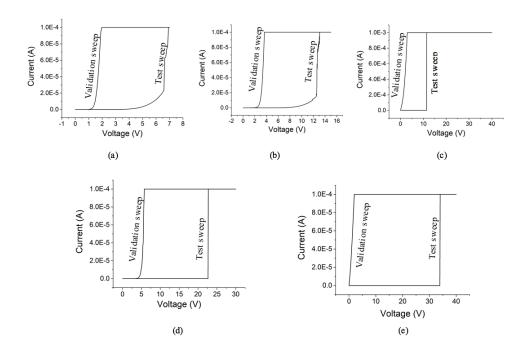

| 3.16         | Cross-sectional view of a two transistor vertical MOSCAP array in GF $22 \ nm$                                                                           |

|              | FDSOI technology with antenna diodes                                                                                                                     |

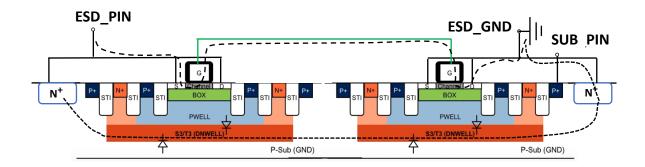

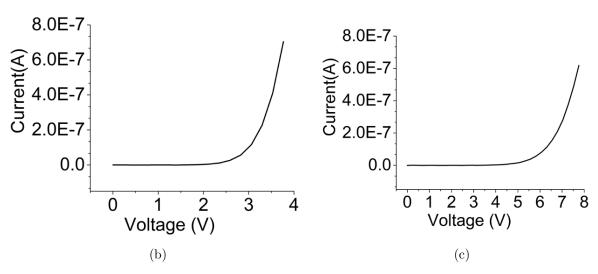

| 3.17         | Experimental I-V characteristic of vertical MOSCAP array                                                                                                 |

| 3.18         | Breakdown characteristics of vertical MOSCAP array                                                                                                       |

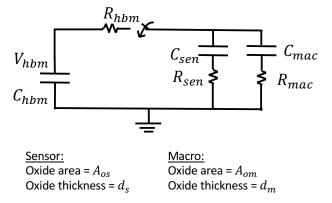

| 3.19         | Theoretical model of ESD sensor for direct contact                                                                                                       |

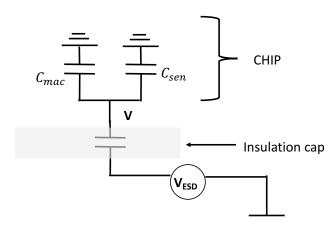

| 3.20         | Theoretical model of ESD sensor in case of field induced charging                                                                                        |

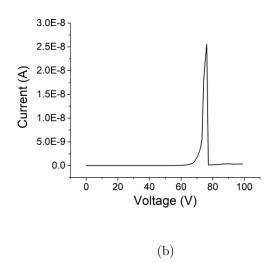

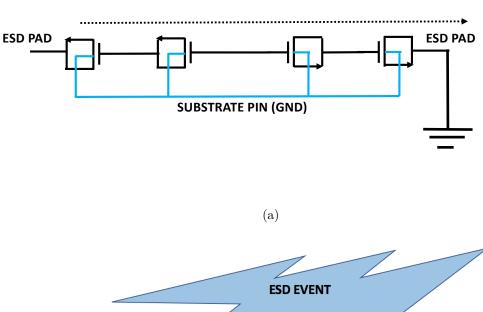

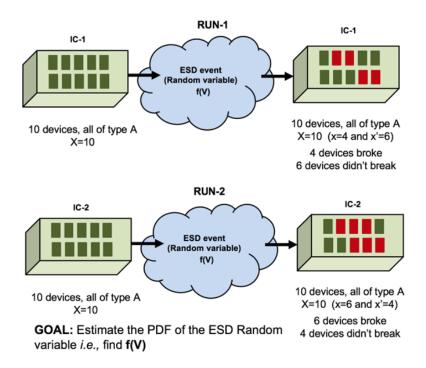

| 11           | IC with ESD gangang paging through an ESD appirentment                                                                                                   |

| 4.1          | IC with ESD sensors passing through an ESD environment                                                                                                   |

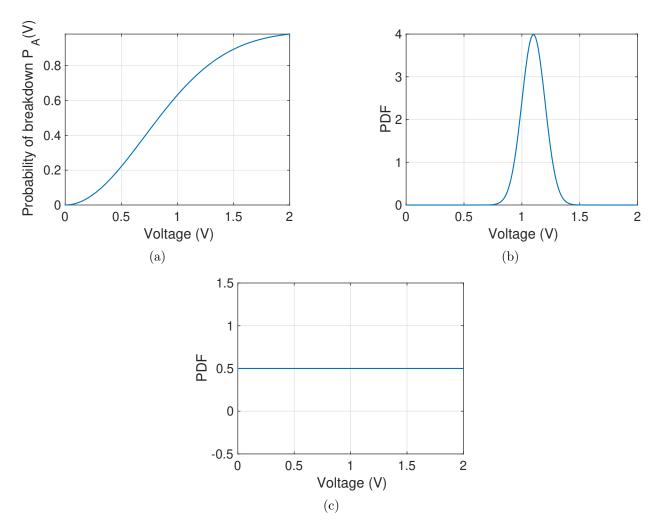

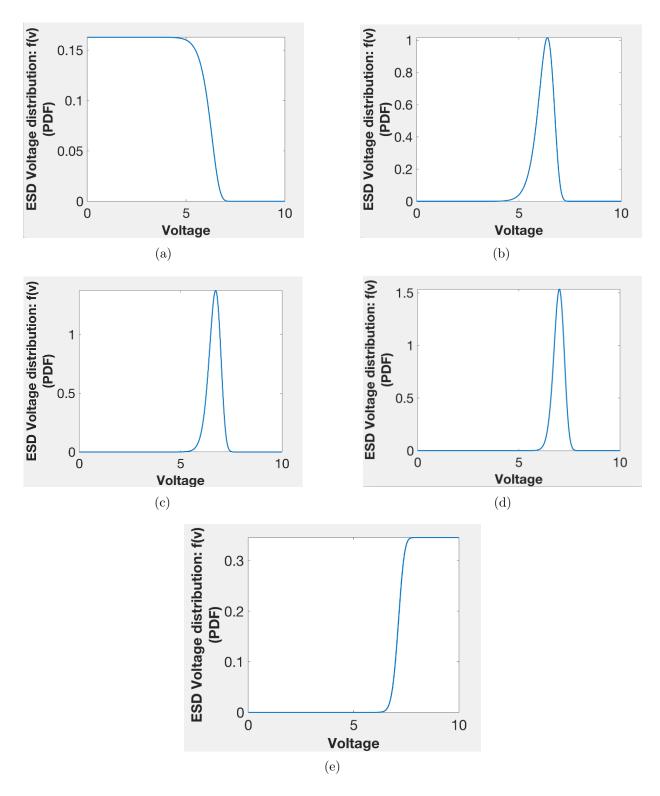

| 4.2          | ESD voltage estimation inputs                                                                                                                            |

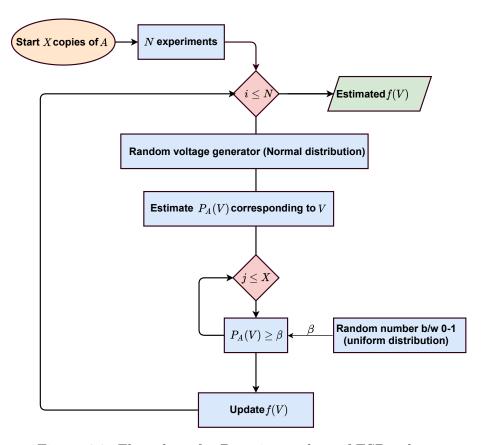

| 4.3          | Flow chart for Bayesian update of ESD voltage                                                                                                            |

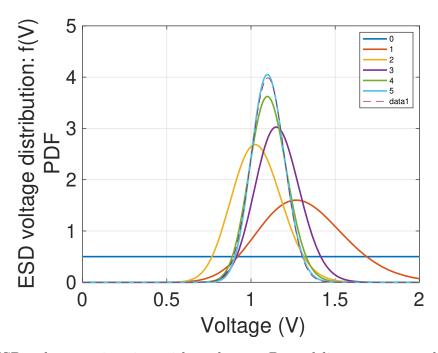

| 4.4          | ESD voltage estimation with each run                                                                                                                     |

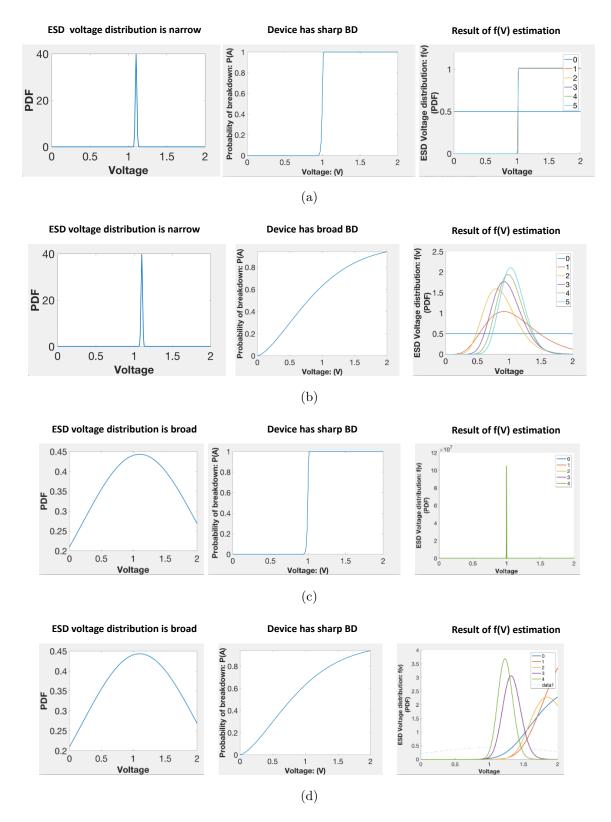

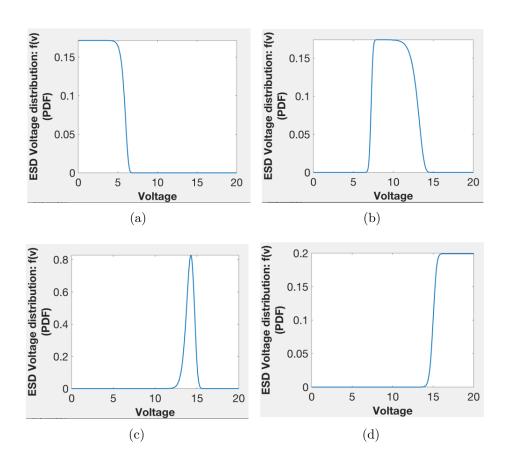

| 4.5          | Different Cases in ESD voltage estimation                                                                                                                |

| $4.6 \\ 4.7$ | ESD gun testing of the sensors                                                                                                                           |

|              | ESD gun in discharge mode                                                                                                                                |

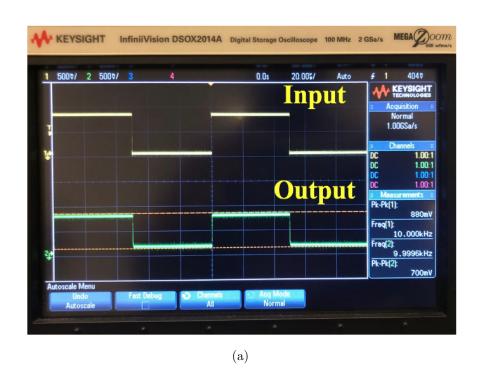

| 4.8<br>4.9   | Test setup for ESD testing at low voltages                                                                                                               |

| 4.9<br>4.10  | Characterization of daisy chain, ESD sensor type-A, type-B before ESD pulse . Characterization of daisy chain, ESD sensor type-A, type-B after ESD pulse |

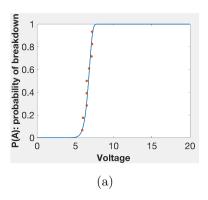

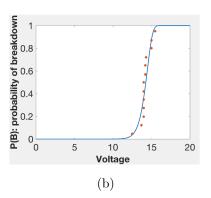

| _            | Probability of breakdown of sensor type-A and sensor type-B                                                                                              |

|              | v - v -                                                                                                                                                  |

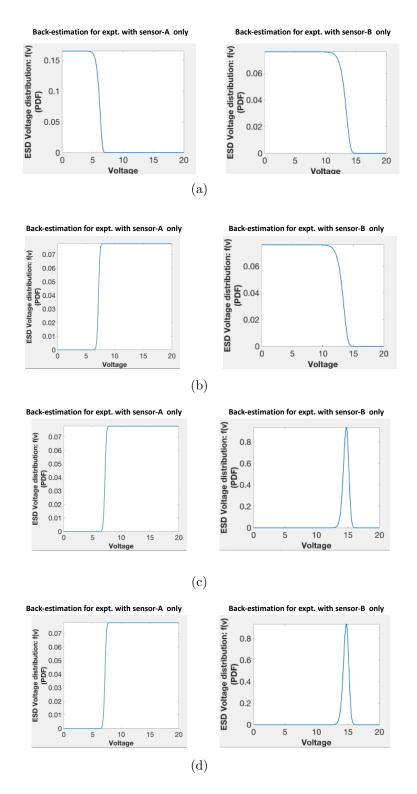

|              | Estimation of ESD voltage using the Bayesian method                                                                                                      |

|              |                                                                                                                                                          |

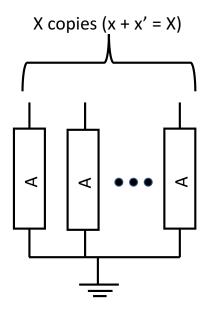

|              | Multiple copies of sensor type-A in parallel in IC                                                                                                       |

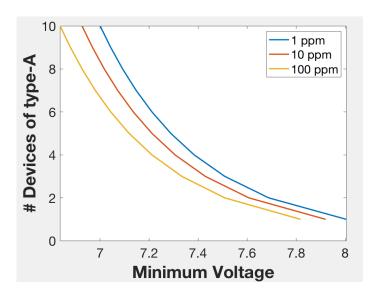

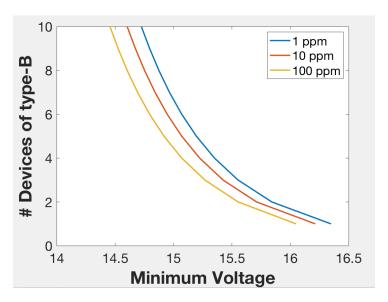

|              | ESD sensitivity graph for sensor type-A                                                                                                                  |

|              | ESD sensitivity graph for sensor type-B                                                                                                                  |

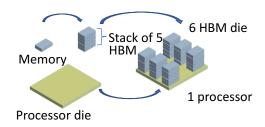

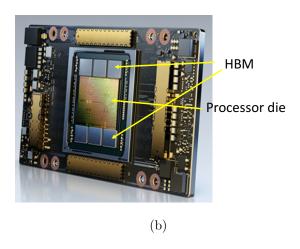

|              | NVIDIA A100 hierarchy                                                                                                                                    |

| 4.18         | Bayesian estimation of the ESD voltage in each possible outcome for the case of                                                                          |

| 1 10         | 4 sensors of type-A                                                                                                                                      |

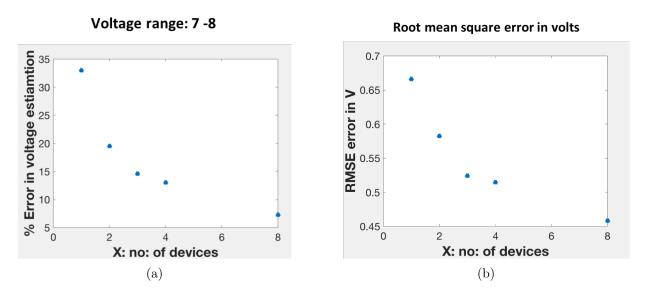

|              | Root mean square error calculation                                                                                                                       |

|              | Monte-Carlo simulation for estimating confidence in ESD voltage measurement.                                                                             |

|              | Root mean square estimation flow chart                                                                                                                   |

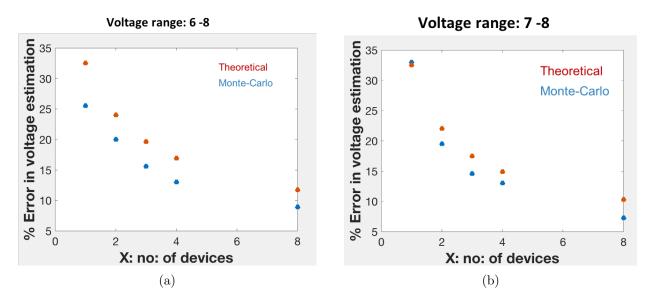

| 4 77         | Confidence estimation from Monte-Carlo similations                                                                                                       |

| 4.23 | Confidence estimation from Monte-Carlo simulations for a smaller voltage interval | 88 |

|------|-----------------------------------------------------------------------------------|----|

| 4.24 | Comparison between Monte-Carlo simulation and Mathematical formulation            | 88 |

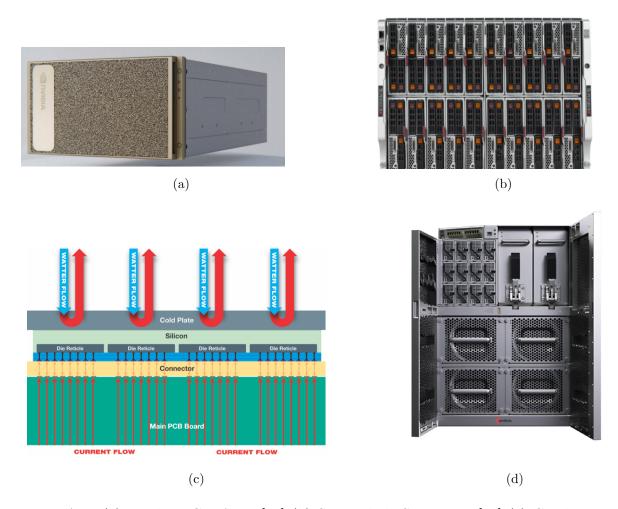

| A.1  | Nvidia DGX A100, SuperBlade SBE-820H, and Cerebras wafer-scale-processors         | 94 |

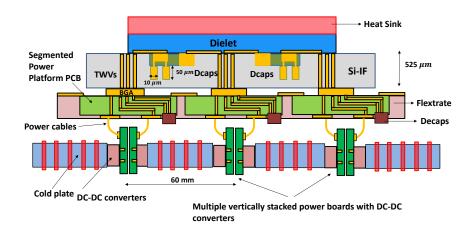

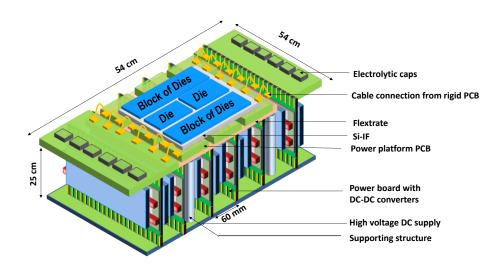

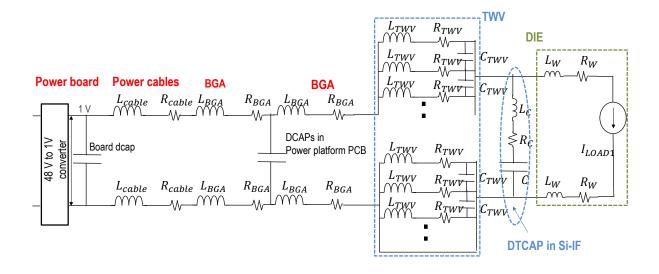

| A.2  | Cross-sectional view of PDN                                                       | 96 |

| A.3  | 3-D view of PDN                                                                   | 96 |

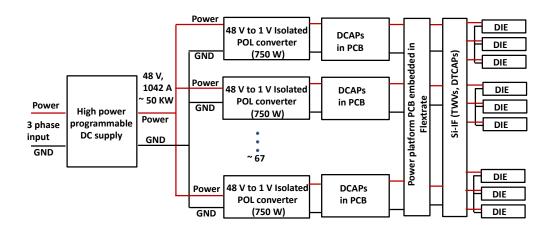

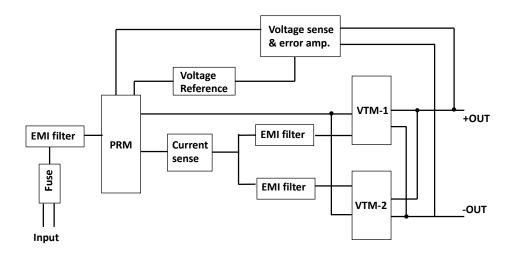

| A.4  | Block diagram of the PDN                                                          | 97 |

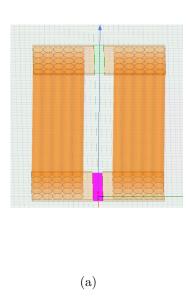

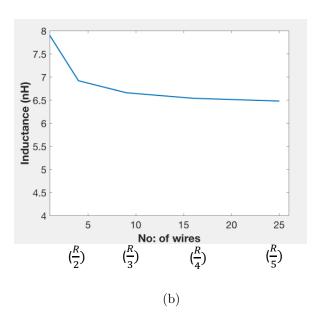

| A.5  | ANSYS HFSS model of multi-strand wire                                             | 98 |

| A.6  | Circuit model of PDN                                                              | 99 |

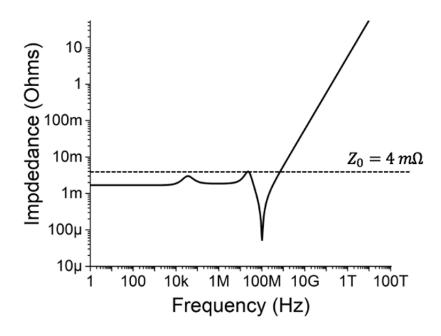

| A.7  | Impedance spectrum of PDN                                                         | 00 |

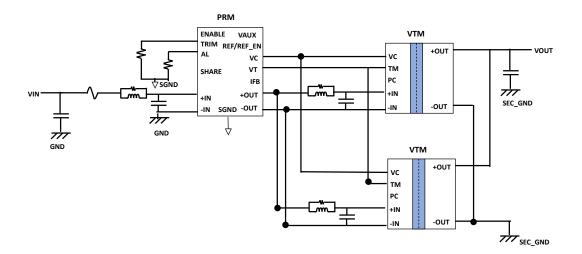

| A.8  | Circuit schematic of PRM driving 2 VTMs in power board                            | 02 |

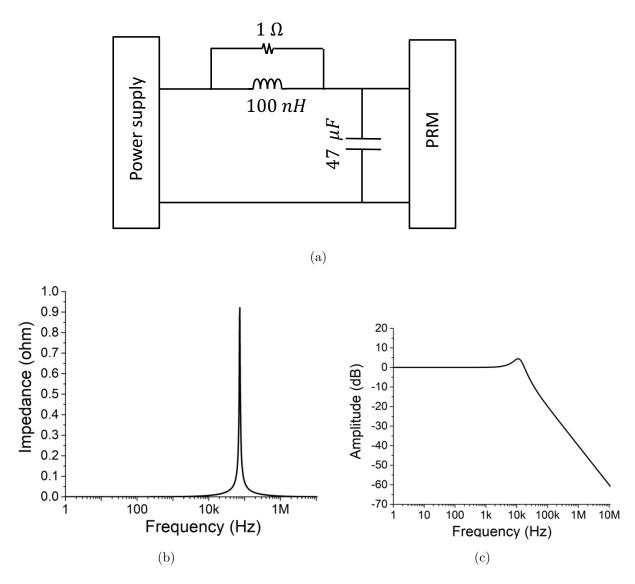

| A.9  | EMI filter between power source and VTM                                           | 03 |

| A.10 | Remote sense mode of operation with PRM and VTMs                                  | 04 |

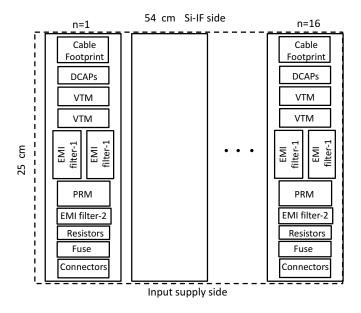

| A.11 | Footprint of the power board                                                      | 04 |

| A.12 | Prototype power board                                                             | 05 |

| A.13 | Output voltage at the VTM for a 9 milli-ohm load                                  | 06 |

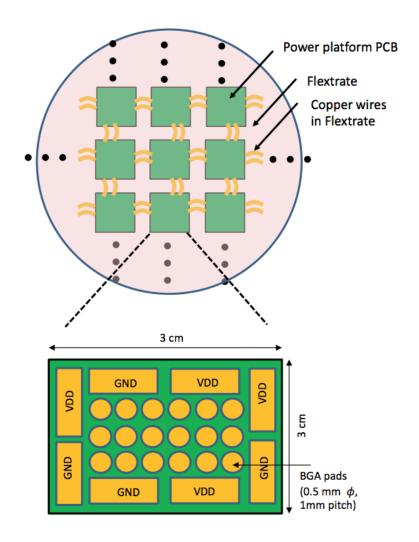

| A.14 | Power platform PCB embedded in Flextrate                                          | 08 |

# List of Tables

| 3.1 | Extracted capacitance values for 25 mm metal coin calibration                 | 39  |

|-----|-------------------------------------------------------------------------------|-----|

| 4.1 | ESD testing with sensors and active macros. Broken devices are denoted by the |     |

|     | $\checkmark$ symbol and not-broken by the × symbol                            | 70  |

| 4.2 | Standalone ESD testing of sensors-A                                           | 70  |

| 4.3 | Standalone ESD testing of sensors-B                                           | 70  |

| 4.4 | Standalone ESD testing of Macro                                               | 71  |

| 4.5 | ESD testing with sensors A and B in parallel                                  | 71  |

| A.1 | R and L contribution per pair of a BGA contact (each BGA has 5 TWVs)          | 98  |

| A.2 | Prototype results of power board                                              | 106 |

## Acknowledgments

First of all, I would like to express my sincere gratitude to my advisor, Prof. Subramanian Iyer for his guidance and support throughout my Ph.D. program. Prof. Iyer has been a tremendous role model and has always inspired me with his innovative thinking and excellent advice. I was fortunate to work under a professor like him with highest calibre and vast industry experience. Thank you Prof. Iyer. I also like to express my deep gratitude to all my committee members, Prof. Ali Mosleh, Prof. Chee Wei Wong, Prof. Dwight Streit for their valuable time, discussions and suggestions over the years.

It was a privilege for me to work in a research group with extremely talented people. I thank Dr. Boris Vaisband for being an excellent mentor and for his inspirational stories that always motivated me. I would like to thank my colleagues at UCLA for helping me along the way. This list includes but is not limited to Goutham Ezhilarasu, Siva C. Jangam, Niloofar Sharookzadeh, Krutikesh Sahoo, Arsalan Alam, Randall Irwin, Ujash Shah, Dr. Adeel Bajwa, Jon Cox, Yu-Tao, Steven Morane, Zhe Wan, Pranav Ambhore, Eric Sorensen, Saptadeep Pal, and Dr. Samatha Benedict. I would also like to thank Kyle Jung, our group admin for his help and support. I also thank my friends Ariyam Das, Arun Sankar, and Joshin P.K. for the insightful discussions, encouragement, and moral support over the last few years. Last but no the least, I would like to thank my mother Chandrika G., my wife Drishya Dhruvan, and my brother Vishnu K.T. for their unconditional love and belief in me. Thank you, Amma, Drishya and Vishnu. I also like to thank my six year old niece and nephew Diya and Deepu. They made me realize that happiness is actually found in simple things!

I thank UCLA Nanolab Research Facility, Integrated Systems Nanofabrication Clean-room, Center for High-Frequency Electronics for their help and support. I would also like to thank UCLA CHIPS consortium, Semiconductor Research Corporation (SRC) JUMP ASCENT, DARPA and other industry sponsors that funded my research. Parts of this dissertation is adapted from several publications during my Ph.D. program.

### Vita

| 2006-2010 | Bachelor of Technology in Electronics and Communication Engineering, |

|-----------|----------------------------------------------------------------------|

|           | College of Engineering Trivandrum, Kerala University, India.         |

| 2011-2013 | Master of Technology in Electrical Engineering,                      |

|           | Indian Institute of Technology Kanpur, India.                        |

| 2013-2014 | Component Design Engineer, INTEL, Bangalore, India.                  |

| 2015-2016 | Ad hoc Lecturer, National Institute of Technology Calicut, India.    |

### **Publications**

Kannan K.T., Subramanian Iyer, "Novel high-power delivery architecture for heterogeneous Integration systems", IEEE 71st Electronic Components and Technology Conference (ECTC), June 1-4, 2021, San Diego, CA.

Kannan K.T., Subramanian Iyer, "ESD challenges in Wafer Scale Systems", Govt. Microcircuit Applications and Critical Technology Conference (GOMACTech), Virtual conference, March 29-April 1, 2021.

Ujash Shah\*, Kannan K.T.\*, Timothy S. Fisher, Subramanian Iyer, "Power Delivery and Thermal Management for Heterogeneous Wafer-scale Systems", Govt. Microcircuit Applications and Critical Technology Conference (GOMACTech), Virtual conference, March 29-April 1, 2021 (\* denotes equal contribution)

Kannan K.T., Subramanian Iyer, "Deep Trench capacitors in Silicon Interconnect Fabric", IEEE 70th Electronic Components and Technology Conference (ECTC), May 26-29, 2020, Lake Buena Vista, FL.

Kannan K.T., Boris Vaisband, Subramanian Iyer, "On-Chip ESD Monitor", IEEE 69th Electronic Components and Technology Conference (ECTC), May 28-31, 2019, Las Vegas, NV.

Kannan K.T., Adeel Bajwa, Boris Vaisband, Siva C. Jangam, Subramanian Iyer, "Reliability Evaluation of Silicon Interconnect Fabric Technology", IEEE International Reliability Physics Symposium (IRPS), March 31-April 4, 2019, Monterey, CA.

Siva C. Jangam, Adeel Bajwa, Kannan K.T., Premsagar Kittur, Subramanian S. Iyer, "Electrical Characterization of High Performance Fine Pitch Interconnects in Silicon Interconnect Fabric", IEEE 68th Electronic Components and Technology Conference (ECTC), May 29-June 1, 2018, San Diego, CA.

Siva C. Jangam, Adeel Bajwa, Kannan K.T., Subramanian S. Iyer, "Characterization of Fine-Pitch Interconnections ( $\leq 10 \mu m$ ) on Silicon Interconnect Fabric for Heterogeneous Integration", International Symposium on Microelectronics, Vol. 2018. No. 1. International Microelectronics Assembly and Packaging Society(IMAPS), May 29-June 1, 2018, San Diego, CA.

# Chapter 1

# Introduction

# 1.1 Electrostatic discharge

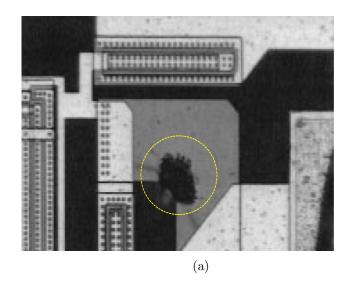

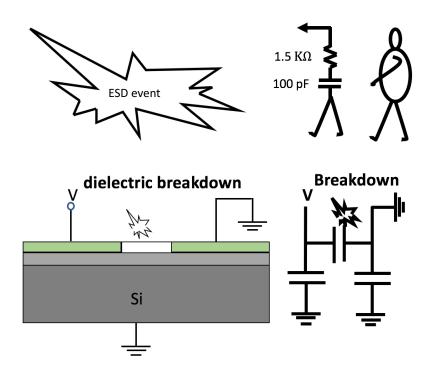

Electrostatic discharge (ESD) has become one of the most prevalent problems in the semi-conductor industry. ESD happens everywhere – industry, home, business, during transport and so on. ESD occurs due to electrostatic charge transfer between two components in close proximity with voltage imbalance. ESD can be initiated by a direct contact or a dielectric breakdown between the two components. As a result of an ESD event, a high transient current (up to few tens of Amps) and large voltage (up to several tens of kV) can develop between the two components. This fast ( $\sim 150~ns$ ) transient phenomenon can cause serious damage or degrade the performance of affected ICs [1]. ESD is different from electromagnetic interference (EMI) which occurs due to electric and magnetic field coupling between a source and a victim equipment/ device (the field coupling can be through radiation, inductive/capacitive or direct contact). An ESD event can cause local damage to metals, oxides, junctions, and other device components (Fig. 1.1), resulting in either complete or partial device failure [2]. About 35 % of the IC field returns are reported to be ESD induced, with annual costs estimated to be several billions of dollars [1, 3].

There are three principle sources of charge [2] which can give rise to damaging ESD

Figure 1.1: Damage in ICs [3, 4] (a) Blown polysilicon resistor due to ESD (b) Ruptured gate oxide

#### events:

- 1. A charged person/equipment coming in contact with a device and discharging the stored charge to or through the device to ground. People and equipment can become charged while interaction (contact and separation) with another object/material. For example, a person walking on a floor can generate voltages up to 4 kV depending on the footwear used [5, 6]. When the person comes in contact with an electronic device, charge transfer to the device can occur, possibly causing device malfunction.

- 2. The device itself can act as one plate of a charged capacitor. When the device comes in contact with an effective ground, the discharge pulse can create damage to the device.

- 3. A device in the electrostatic field associated with a charged object. The device in this field can have a potential induced across it, and upon contact with a grounded surface, electric discharge can occur, which may cause damage.

Maxwell's method [7] is used to analyse and determine device potentials and the transfer of charge during typical discharges. A system involving n multiple conductors can be

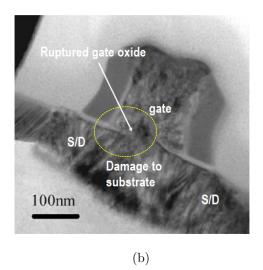

Figure 1.2: Charged human body and floating device (a) approach (b) contact. Adapted from [7]

described by the Maxwell's equations as

$$Q_{1} = C_{11}V_{1} + C_{12}V_{2} + \dots + C_{1n}V_{n},$$

$$Q_{2} = C_{21}V_{1} + C_{22}V_{2} + \dots + C_{2n}V_{n},$$

$$\dots$$

$$Q_{n} = C_{n1}V_{1} + C_{n2}V_{2} + \dots + C_{nn}V_{n},$$

where  $C_{11}, C_{22}, ... C_{nn}$  etc are the coefficients of self-capacitance, and  $C_{12}, ... C_{1n}$  etc are coefficients of mutual capacitance. As an example, consider, the following case where a human body with insulated shoes walking over a carpet is approaching a semiconductor device. Triboelectrification between the carpet and shoes results in shoes getting charged to equal and opposite polarity to charge on carpet. Two cases are possible: (i) The semiconductor device is floating and (ii) The semiconductor device is grounded.

Case-1 (device is floating): The system of Maxwell's equations are given below for the human body approaching the device [7]. Here body-1 refers to human body, body-2 refers to the shoes, and body-3 refers to the device, as shown in Fig. 1.2(a)

$$0 = C_{11}V_1 + C_{12}V_2 + C_{13}V_3 \tag{1.1}$$

$$Q_2 = C_{21}V_1 + C_{22}V_2 \tag{1.2}$$

$$0 = C_{31}V_1 + C_{33}V_3 \tag{1.3}$$

If it is assumed that there is negligible coupling of electric flux from body-2 to body-3  $(C_{23} = C_{32} = 0)$ , the bulk of electric flux associated with body-2 (shoes) couples to body-1  $(C_{12} = -C_{22})$ , and the bulk section of human body is greater compared to the shoes  $(C_{11} > C_{22})$

$$V_1 - V_3 = \frac{Q_2(1 + C_{13}/C_{33})}{C_{11} - C_{13}^2/C_{33}}$$

(1.4)

Assuming body-3 to be small compared to body-1, this implies that  $C_{13} = -C_{33}$  which makes the potential difference  $V_1-V_3$  to be zero. So, for the charged human body approaching a floating integrated circuit, a discharge will probably not occur. When contact is made between body-1 and body-3 as shown in Fig. 1.2(b) the system of equations gets modified as follows:

$$q_1 = C_{11}V_1 + C_{12}V_2 + C_{13}V_3 (1.5)$$

$$Q_2 = C_{12}V_1 + C_{22}V_2 (1.6)$$

$$q_3 = C_{13}V_1 + C_{33}V_3 (1.7)$$

But  $V_1 = V_3 = V$ , and  $q_1 + q_3 = 0$ , thus the system equations can be rewritten as:

$$q_1 = C_{11}V + C_{12}V_2 + C_{13}V (1.8)$$

$$Q_2 = C_{12}V + C_{22}V_2 (1.9)$$

$$q_3 = C_{13}V + C_{33}V (1.10)$$

The solution then yields:

$$V = \frac{-C_{12}/C_{22}Q_2}{C_{11} + 2C_{13} + C_{33} - C_{12}^2/C_{22}}$$

(1.11)

Plugging in  $C_{12} = -C_{22}$  and  $C_{11} \gg C_{22}$ :

$$q_3 = \frac{(C_{13} + C_{33})Q_2}{C_{11} + 2C_{13} + C_{33}} \tag{1.12}$$

If body-3 is very small compared body-1 ( $C_{13} = -C_{33}$ ), the charge transfer q3 then approaches zero.

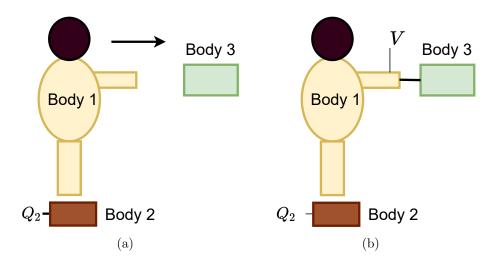

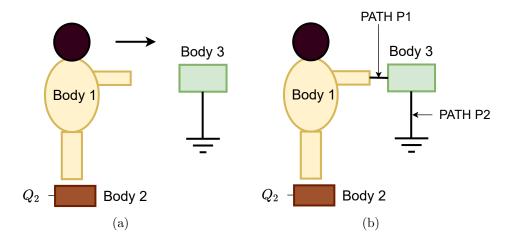

Case-2 (device is grounded): When body-3 is grounded, the system of Maxwell's equation Fig. 1.3(a) can be written as:

$$0 = C_{11}V_1 + C_{12}V_2 (1.13)$$

$$Q_2 = C_{12}V_1 + C_{22}V_2 (1.14)$$

$$Q_3 = C_{13}V_1 \tag{1.15}$$

Here it is assumed that there is negligible coupling of electric flux from body-2 to body-3  $(C_{23} = C_{32} = 0)$ . Body-1 potential then comes out to be:

$$V_1 = \frac{Q_2}{C_{12} - (C_{11}C_{22})/C_{12}} \tag{1.16}$$

For typical applications where:  $C_{12} = -C_{22}$  and  $C_{11} \gg C_{22}$ :

$$V_1 = \frac{Q_2}{C_{11}} \tag{1.17}$$

As body-1 approaches body-3, the discharge can be modelled by a fine conductor connecting the two bodies (Fig. 1.3(b)). Body-1 and body-3 are now at same ground potential. The system of equations then becomes:

$$Q_1 = C_{12}V_2 (1.18)$$

$$Q_2 = C_{22}V_2 (1.19)$$

$$Q_3 = C_{23}V_2 = 0 (1.20)$$

$$Q_1 = \frac{C_{12}Q_2}{C_{22}} \tag{1.21}$$

Figure 1.3: Charged human body and grounded device (a) approach (b) contact. Adapted from [7]

if

$$C_{12} = -C_{22}$$

,

$$Q_1 = -Q_2 \tag{1.22}$$

The charge transferred to the device would be  $-Q_2$ . If the device is approached in a grounded state, a charge equal to that trapped on the shoes of the human body is transferred. In summary, the potential difference between the device and the conductor before contact, and the amount of charge transferred during the contact, depend on the system capacitance coefficients and the electrical state of the conductor [7, 8].

### 1.1.1 ESD models

To emulate real life ESD events, ESD models are used. Three basic models are used: (i) the human body model, (ii) machine model, and (iii) charged device model.

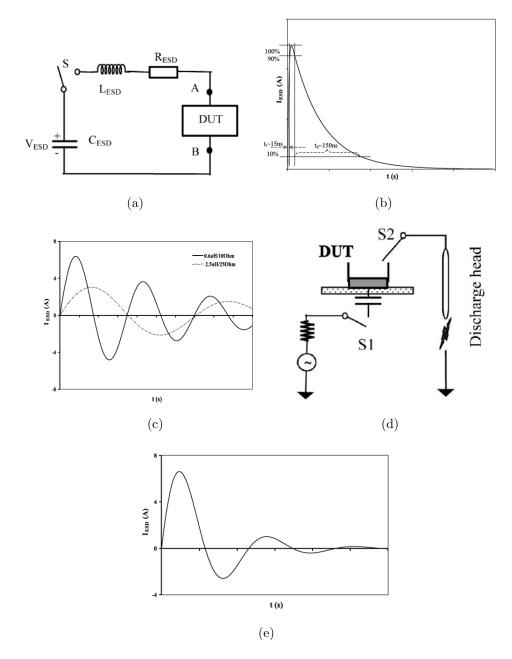

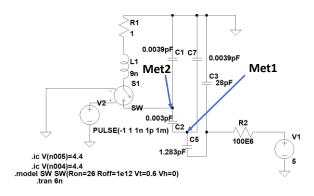

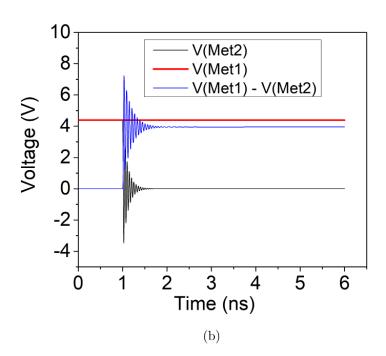

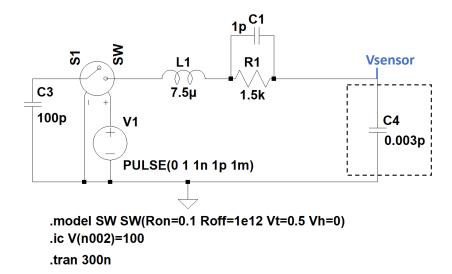

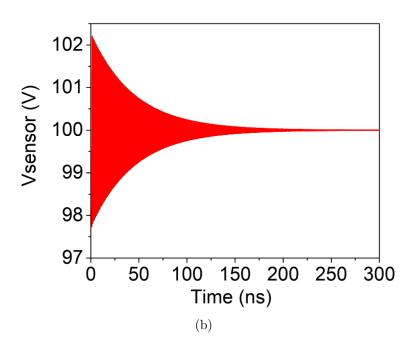

The human body model (HBM) emulates a charged human body coming in contact with an electronic device. HBM is modelled by a 150 pF capacitor, which is charged to a high-voltage and then discharged by a switch(S) through a 1-2  $k\Omega$  series resistor to the device under test to ground. The test setup and typical waveform for an HBM [1] is shown in Figure 1.4

Figure 1.4: ESD models [1] (a) Test setup for HBM and MM (b) Typical HBM discharge waveform (c) Typical MM discharge waveform (discharge voltage level  $\sim 400$  V) (d) Test setup for CDM (e) Typical CDM discharge waveform at a discharge level of 1100 V

The machine model (MM) emulates the case where a charged machinery comes in contact with the IC, for example during automated process in IC production and assembly. A MM test setup consists of a high-voltage supply in series with a resistor that charges a capacitor (100 pF) to a high voltage. The discharge of the capacitor to the device under test (DUT) occurs on closure of a switch(S) that disconnects the capacitor from the high voltage supply and connects it to the DUT through a negligible resistor and inductor. Typical MM ESD events produce an oscillatory discharging waveform with a high peak current and shorter rise time as compared to the HBM (Fig. 1.4(c)).

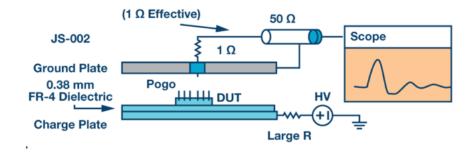

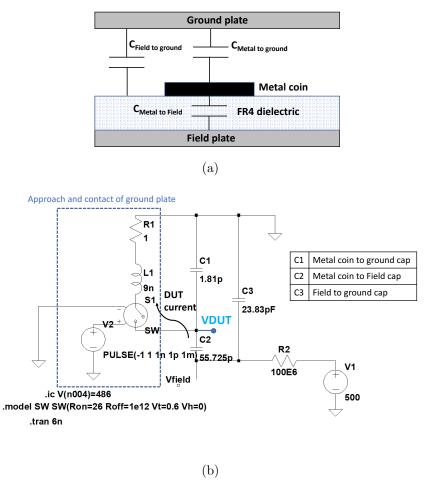

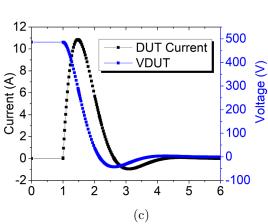

The charged device model (CDM) simulates self-induced discharging of devices where ungrounded electronic parts become charged during manufacturing and assembly and later discharge to a grounded surface. A CDM test setup is shown in Figure 1.4(d). Initially, switch S1 is closed and S2 is open which charges the DUT to a high voltage. In the second stage, S1 is open and S2 is closed which discharges the DUT pin. CDM typically has a fast impulse-like waveform as shown in Figure 1.4(e). In CDM, charge originates within the device due to self-induced charging and subsequent discharging through the pin. In HBM and MM, the charges originate from an external source. Device internal protection structures sometimes becomes ineffective against CDM due to the internal charge generation. Voltage drops experienced during CDM due to the transient high current can damage the internal structure of a device [1, 9].

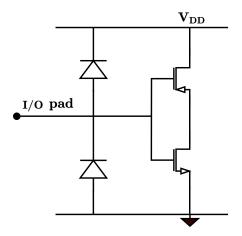

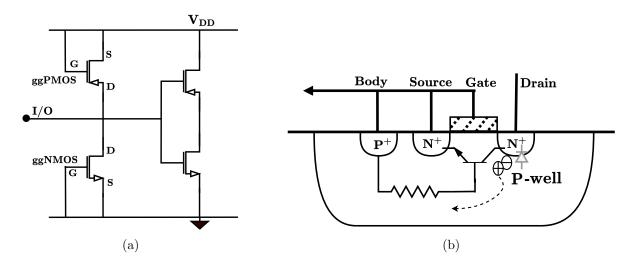

## 1.1.2 ESD protection

Fundamentally, two approaches are employed in protecting electronic devices from ESD: (i) reducing likelihood of ESD and (ii) adding ESD protection circuitry on to the electronic devices. ESD occurs as a result of a voltage imbalance. An ESD event occurs in four stages: 1) generation of charge, 2) transfer of charge due to voltage imbalance, 3) conduction of charge, and 4) damage due to charge transfer and associated transient current and voltage. In order to reduce the likelihood of ESD, charge generation mechanisms which causes ESD have

to be reduced. The first method involves use of protection equipment to control generation of static charges. This includes room ionizers, local ionizers, ESD wrist straps etc. The second method adds additional circuit elements on ICs which provides an alternate path for charge conduction in case of an ESD event [10, 11].

### 1.1.2.1 Workstation and room level ESD controls

An ESD event occurs when there is a voltage difference between two bodies and a low impedance connection exists between the two bodies, allowing for charge transfer which may cause damage to one or the two bodies involved. If the voltage difference between the two bodies is small, minimal charge transfer happens. Similarly, if the impedance connecting the two bodies is high, charge transfer might not happen. These two principles are used in ESD prevention mechanism i.e., to make the generated/developed voltage to be low enough and to provide a high impedance path between the two bodies, so that minimal charge transfer happens [10].

Moisture content in the air plays a key role in determining the magnitude of charge developed on an object, as it defines the electrical resistance of the air. In dry areas, large charge build-up can happen before they are dissipated. If the moisture content is high, charge is bled off through the air easily. If the moisture content is low, it allows for the charge to increase on objects without being dissipated. ESD events are more common in winter because the air is dry and the moisture content is low in air, which allows for charge build-up and generation of high ESD voltages. The typical safe working range of relative humidity is 30-70 % [12, 13].

Air conductivity can be controlled by injecting conductive species in the air. In order to ensure that no net charge is introduced, charges must be injected in balance (equal number of positive and negative charges). Room ionizers are used to do this, and they basically remove static charges from surfaces that cannot be grounded. Ionizers neutralize objects and people entering a work area. The two important aspects of air ionizers are: (i) charge

neutralization time, which is the time require to neutralize a given amount of charge by the ionizer, and (ii) ion-imbalance, which provides a measure of ionizers' ability to generate an equal amount of positive and negative charges. If there is an imbalance, potential gradients form in the air, impacting the ionizer performance [10, 14].

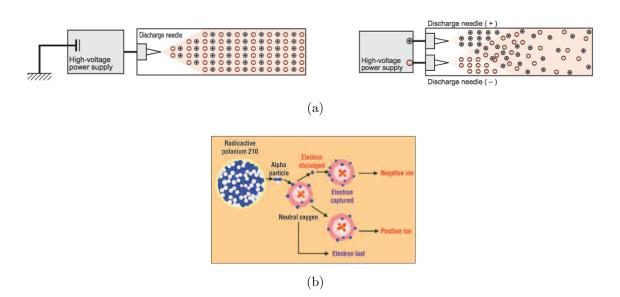

Ionizers are classified based on the method used for charge generation — electrical or nuclear. Electrical ionizers can further be classified into AC and DC ionizers (Figure 1.5(a)). In AC ionizers, an AC voltage is applied to the discharge needles and produces positive ions and negative ions alternately in each half cycles. In DC method, either positive or negative ions are produced depending on the polarity of the DC voltage applied. Thus both positive and negative voltage sources are required to maintain charge neutrality. AC method creates positive ions and negative ions efficiently and generates a stable environment with high ion flux density. However, the DC method generates positive ions and negative ions constantly and doesn't include a generation cycle like the AC method. Thus the neutralization rate of DC ionizer is faster [15]. Nuclear ionizers use a nuclear source for ionization. For example, an Alpha ionizer (Figure 1.5(b)) utilizes the nuclear source Polonium 210, which emits alpha particles. The alpha particles (helium nucleus) collide with air molecules, and knock out electrons over a distance approximately 3 cm [16]. Alpha ionization is used commercially for applications involving explosive or flammable environments.

Typical ionizers include over-head ionizers [17], bench top ionizers [18], and gun ionizers [19] as shown in Figure 1.6. These can cover high voltage ranges (1000s of Volts) with a balance of  $\pm$  1 Volt and a discharge time in the range of few seconds (time taken by the ionizer to discharge a test object from 1000 V to 100 V)

Other major sources of charging in a manufacturing area are floors and carpets [20]. Here the use of anti-static finishes can reduce charge generation. The surface should neither induce a static charge on the parts nor provide a rapid discharge path [10]. The workstation should be designed so as to minimize static charge generation and transfer (Fig. 1.7). The use of highly conductive work surfaces (for example stainless steel) can create a hazard. This is because a metal/ high conductive surface can act as a large charge sink without any

Figure 1.5: Types of ionizers  $[15,\ 16](a)$  DC and AC static ionizers (b) nuclear ionizer principle

Figure 1.6: Over-head [17], bench top [18] and gun ionizers [19] (from left to right)

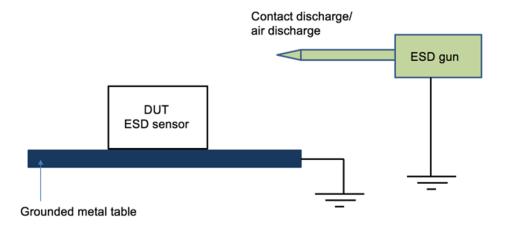

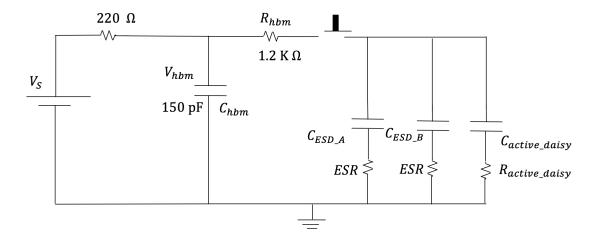

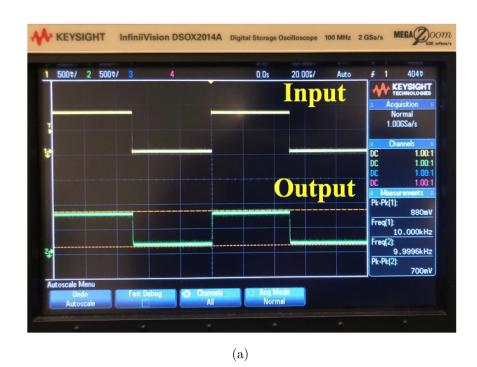

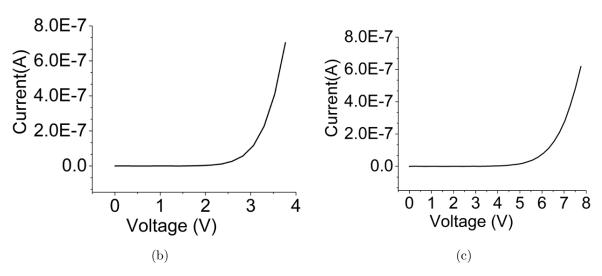

significant change in its potential and a rapid discharge from a charged object to metal/high conductive surface due to the potential difference may create spark/hazards. A static dissipative surface with a sheet resistance of  $10^5-10^9$   $\Omega/\Box$  is effective in providing an ESD safe environment [21, 22].